Although hello is a very simple program, all major parts of the system must work together for it to run to completion. As we follow the life of the program, we will briefly introduce the key concepts, terminology and components involved. On the other hand, integer computer arithmetic fulfills many of the familiar properties of real integer arithmetic.

For example, multiplication is associative and commutative, so computing any of the following expressions C yields On the other hand, floating point arithmetic is not associative due to the finite precision of the representation.

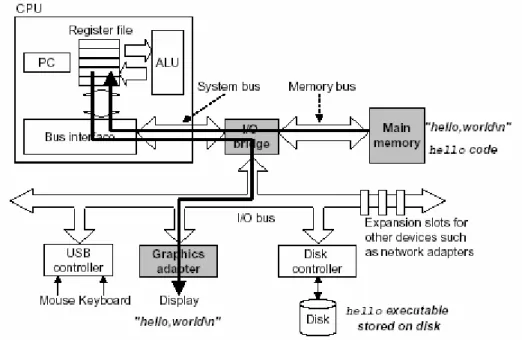

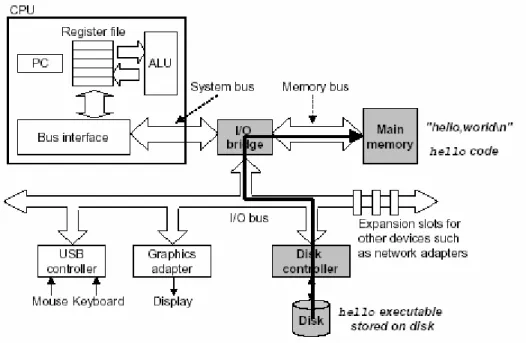

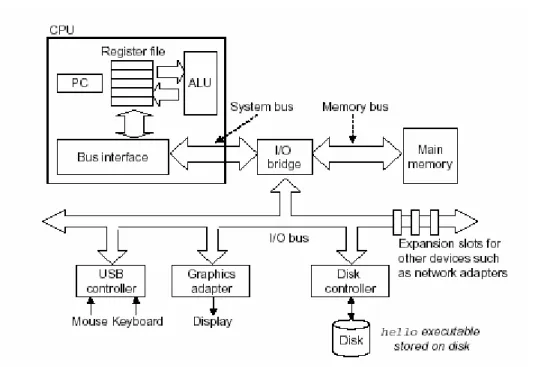

- Hardware Organization of a System

- Níveis de abstracção num computador e mecanismos de conversão

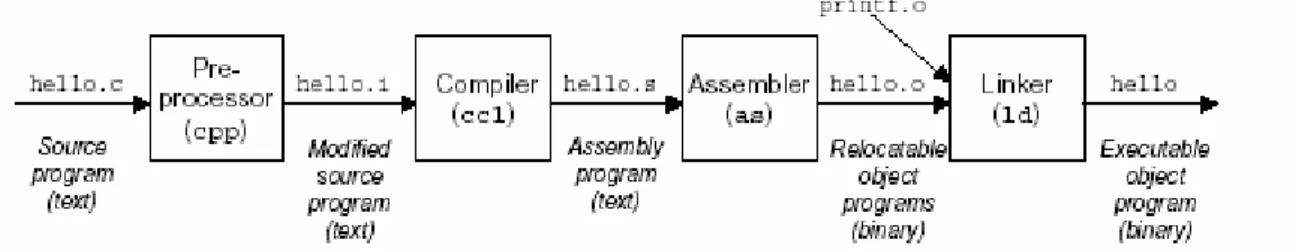

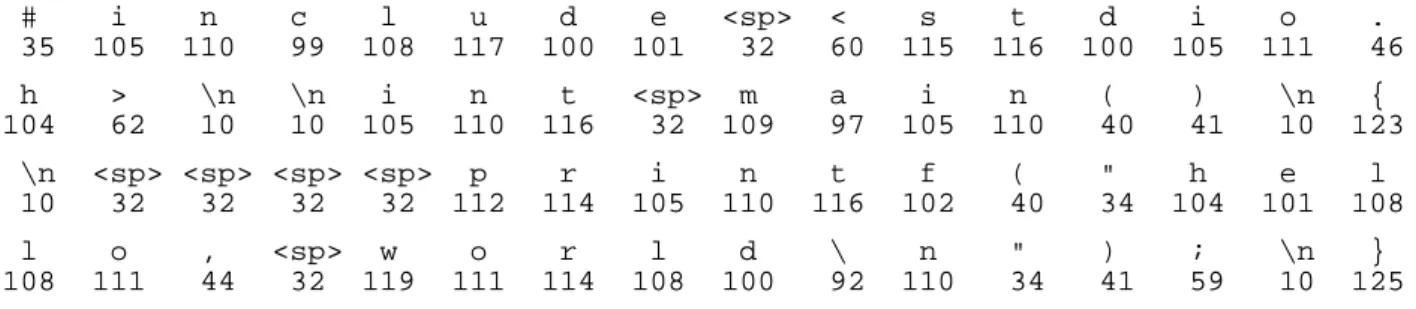

- Programs are Translated by Other Programs into Different Forms (retirado de CSAPP) The hello program begins life as a high-level C program because it can be read and understood by

- Processors Read and Interpret Instructions Stored in Memory

- Running the hello Program

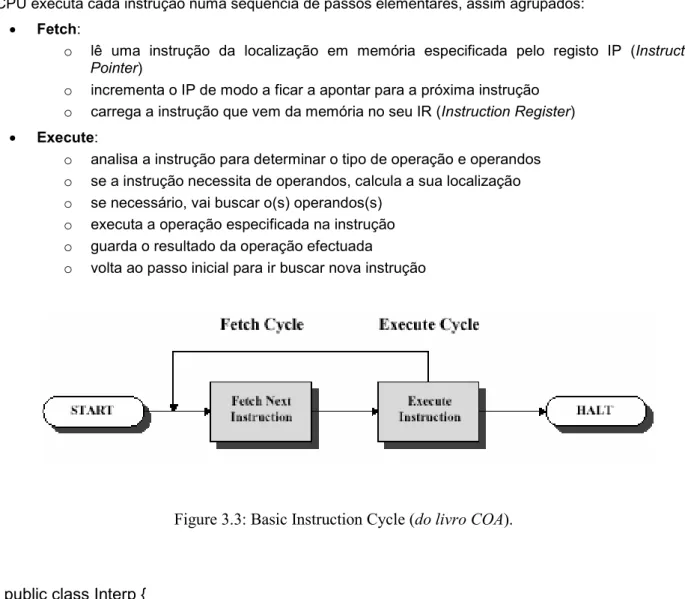

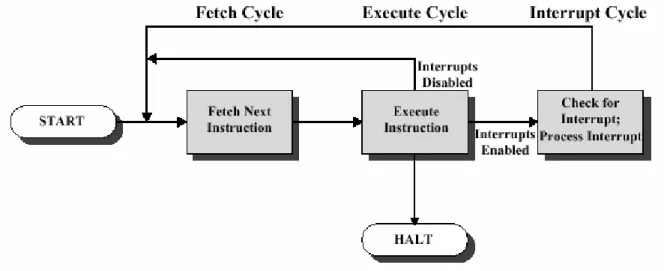

- Execução de instruções num computador

- Acessos à memória na execução de instruções

- Accessing Main Memory (retirado de CSAPP)

- Instruction-Level Parallelism (retirado de SCO)

- Caches Matter (retirado de CSAPP)

- Storage Devices Form a Hierarchy (retirado de CSAPP)

- Análise do nível ISA (Instruction Set Architecture)

- Operações num processador

We will get to its various details in stages over the course of the book. Load: Copies a byte or a word from main memory to a register, overwriting the previous contents of the register. Jump: Extracts a word from the instruction itself and copies that word to the program counter (PC), overwriting the previous value from the PC.

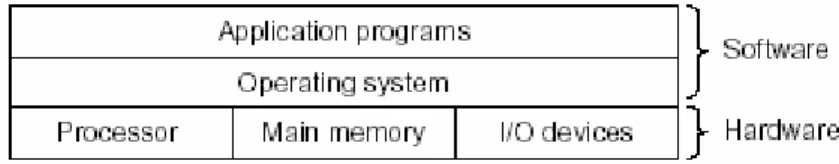

Note that our greeter calls the printf function, which is part of the C standard library that every C compiler provides. And in Chapter 6, you'll learn about the hierarchical nature of the memory system, how C compilers store data fields in memory, and how your C programs can they use this knowledge to operate more efficiently. An operating system can be thought of as a software layer sandwiched between an application program and hardware, as shown in Figure 1.10.

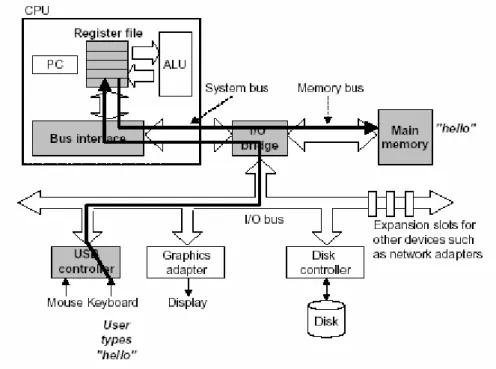

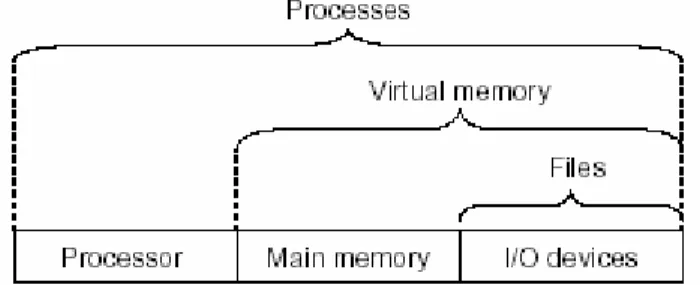

An operating system achieves both goals through the fundamental abstractions shown in Figure 1.11: processes, virtual memory, and files. The I/O bridge translates system bus electrical signals into memory bus electrical signals. Then the main memory detects the address signal on the memory bus10, reads the address from the memory bus, retrieves the data word from the DRAM, and writes the data to the memory bus11.

Finally, main memory reads the data word from the memory bus and stores the bits in DRAM (Figure 6.8(c)). In the former, parallelism is exploited within individual instructions to extract more instructions/s from the machine. To be able to run in parallel, two instructions must not conflict in terms of resource usage (eg registers) and neither must depend on the output of the other.

As with a single pipeline, either the compiler must guarantee that this situation holds (ie, the hardware does not check and returns incorrect results if the instructions are incompatible), or conflicts are detected and eliminated at runtime using additional hardware . As we move from the top of the hierarchy to the bottom, devices become slower, larger, and less expensive per byte.

Localização dos operandos

- Formato de instruções em linguagem máquina

- Tipos de instruções presentes num processador

- Registos visíveis ao programador

- Modos de acesso aos operandos

Quando o formato da instrução permite, a especificação dos 3 operandos para realização de operações no processador - seja sua localização ou seu valor - vem diretamente na própria instrução. Quando o custo de memórias e processadores era significativo, os conjuntos de instruções do processador eram compactados para tamanhos pequenos (8 bits), ao custo de comprometimentos no número de operandos a incluir e do uso de instruções de comprimento variável (com consequências desastrosas para a operação do pipeline ). No formato de qualquer instrução em linguagem de máquina, sempre é possível identificar uma série de campos com informações bem definidas: um campo caracterizando a operação a ser realizada (normalmente chamado de opcode) e tantos campos quantos forem os operandos que podem ser especificado.

As figuras a seguir ilustram os 2 tipos de instruções mencionadas acima: uma derivada de uma arquitetura originária dos anos 70 (Pentium II, baseada no 8086/8) e outra de uma arquitetura RISC (MIPS). O conjunto de instruções presente no conjunto de instruções de cada processador (ou família de processadores) é bastante variado. Um dos aspectos essenciais da programação em linguagem de máquina (ou da leitura e compreensão de um programa escrito nesse nível) é saber quantos registradores você tem, qual o tamanho deles e em que circunstâncias esses registradores podem ser usados.

A existência de um grande número de registradores nas arquiteturas RISC, aliada à evolução da tecnologia de compiladores nos últimos anos (principalmente na geração de código), tornou possível representar a maioria das variáveis escalares diretamente nos registradores, sem tantas vezes precisar de memória. Esses processadores tinham um número menor de registradores e consequentemente uma organização diferente que suportava de forma eficiente diferentes mecanismos de acesso à memória. A arquitetura base possui efetivamente 4 registradores para armazenar operandos aritméticos (A, B, C e D), mais 4 para trabalhar com ponteiros de memória (BP, SP, DI e SI) e outros 4 para manipular uma memória segmentada (CS, DS , SS e ES; a única maneira de uma arquitetura de 16 bits acessar mais de 64k células de memória).

A escolha de um desses métodos de acesso é expressa explicitamente no formato de instrução da operação a ser executada pela UCP. Algumas arquiteturas RISC também suportam cálculo de endereços por meio da soma do conteúdo de dois registradores. Como as arquiteturas CISC têm um tamanho de registro menor, elas precisam acessar a memória com mais frequência para recuperar/armazenar o conteúdo das variáveis.

Ordenação de bytes numa palavra

Instruções de input/output

O acesso aos periféricos de um computador normalmente é feito através dos controladores, que são conectados aos barramentos do computador. Esses controladores executam quase todas as tarefas essenciais para o bom funcionamento dos periféricos; eles devem primeiro ser devidamente configurados, depois ativados com comandos específicos e estabelecer comunicação com as informações a serem transferidas de/para o computador. A maioria dos processadores não possui instruções de entrada/saída específicas para executar essas atividades; apenas use as instruções normais de acesso à memória para ler ou escrever nos registradores do controlador.

O decodificador de endereços do computador será responsável por gerar os sinais apropriados de seleção de chip para selecionar o controlador necessário, de acordo com o mapa de alocação de memória definido pelo projetista do computador. Esse modelo de mapeamento do espaço de endereço de entrada/saída no espaço de endereço de memória é chamado de E/S mapeada em memória. Outros processadores, como os da família Ix86, possuem adicionalmente instruções de I/O específicas, que implementam essencialmente uma das 2 operações de acesso a um registrador de um controlador (também chamado de porta): operação de leitura de ' uma porta - em - ou escrevendo em uma porta - fora.

Caracterização das arquitecturas RISC (resumo)

Anexo A: Sistemas de numeração e representação de inteiros

- Sistemas de numeração A.2 Conversão entre bases

- Sistemas de numeração

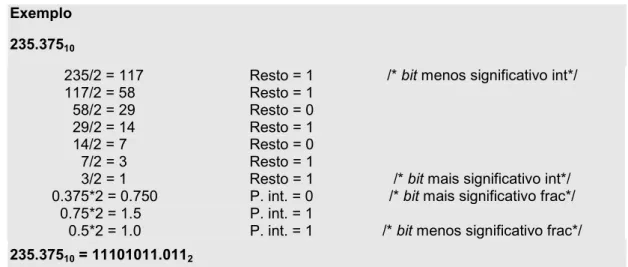

- Conversão entre bases

- Base hexadecimal

- Números negativos

Também ajuda saber como as potências de 2 se comportam para expoentes com mais de um dígito. Como em qualquer outro sistema de numeração - onde o intervalo de valores que podem ser representados por n dígitos é bn - a mesma lógica se aplica à representação de valores binários. O sistema de numeração de base hexadecimal (16) é frequentemente utilizado como forma alternativa de representar valores binários, não só pela facilidade de conversão entre essas 2 bases, mas também pela menor chance de erro humano ao ler/escrever números.

Cada dígito hexadecimal representa um valor entre 0 e 15; cada conjunto de 4 bits também representa um valor no mesmo intervalo. Como o nome indica, a exibição de sinal e amplitude usa um bit para representar o sinal, o bit mais à esquerda: 0 para indicar um valor positivo, 1 para indicar um valor negativo. Na representação de complemento de 1, todos os bits de um número são invertidos para representar seu complemento: convertendo assim um valor positivo em um valor negativo e vice-versa.

Para encontrar o negativo de um número, negue todos os seus bits e adicione um. Como você converte um número representado no complemento de 2 com n bits em um número representado com mais bits. No entanto, a multiplicação e a divisão por potências de 2 são feitas deslocando os bits para a direita e para a esquerda, respectivamente.

Esta regra também se aplica a números em complemento de 2, desde que o sinal seja preservado. Em outras palavras, o valor binário com todos os bits em 0 representa o menor valor inteiro, com ou sem sinal, e o mesmo vale para o maior valor binário, ou seja, com todos os bits em 1: representa o maior inteiro, com ou sem sinal. Como o nome sugere, essa codificação de um inteiro (negativo ou positivo) em binário de n bits é sempre feita em excesso (de 2n-1 ou 2n-1-1).

Anexo B: Representação de reais em vírgula flutuante

- Notação científica

- Normalização na representação

- Intervalo e precisão de valores representáveis B.4 Formato binário dum valor em fp

- O bit escondido

- A norma IEEE 754 para valores em fp

- Notação científica

- Intervalo e precisão de valores representáveis

- Formato binário dum valor em fp

Esse valor é 8 para o expoente - isso permite uma faixa da ordem de grandeza de 1039 - e no mínimo 23 para a parte fracionária - isso permite uma precisão igual a 7 casas decimais. Para realizar qualquer operação aritmética, esses 3 campos precisarão ser identificados e separados para ter um tratamento diferente na unidade que processa os valores em fp. Se o sistema de numeração for decimal, este dígito pode ser um dos 9 dígitos possíveis; se o sistema numérico for binário, esse dígito só pode ser um.

Assim, e apenas na representação binária normalizada, aquele dígito à esquerda da vírgula sempre tem o mesmo valor, e é um desperdício de espaço de memória representá-lo fisicamente. Um bit é ganho para melhorar a precisão, permitindo que o número de bits da parte fracionária seja alterado para 24 (em uma representação de 32 bits). A exibição de valores em fp usando 32 bits e com o formato previamente definido também permite diferentes combinações para exibir o mesmo valor.

Por outro lado, ainda não está definido como representar valores desnormalizados, bem como a representação de valores fora do intervalo permitido com notação normalizada. O padrão IEEE 754 define claramente essas imprecisões e permite maior compatibilidade em termos de dados do tamanho da aplicação entre sistemas que adotam o mesmo padrão. Atualmente, todos os microprocessadores disponíveis comercialmente com unidades fp suportam o padrão IEEE 754 no que diz respeito aos valores de 32 bits.

De diversas formas, o padrão IEEE 754 também prevê a representação de valores em fp que necessitem de uma maior amplitude de representação e/ou melhor precisão. A mais adotada pelos fabricantes usa o dobro do número de bits, 64, por isso também é conhecida como representação de precisão dupla, enquanto a representação de 32 bits é chamada de precisão simples. Para precisão dupla, o padrão especifica, entre outras coisas, que o expoente será representado por 11 bits e a fração por 52 bits.

Anexo C: Arquitectura e conjunto de instruções do IA32

Símbolo Nome Descrição