Performance Analysis of Reversible Fast Decimal Adders

Texto

Imagem

Documentos relacionados

There are three major design goals in reversible logic. 1) The quantum cost, which is the number of 1*1 and 2*2 reversible calculations necessary to generate the

With the analysis of the spatial variability of the data, it was observed that the pens positioned in the central region of the two facilities had the least stressful places

The resistance-in-series analysis identified external fouling on the surface of both membranes, but the tubular membrane showed higher reversible fouling, while the reversible

In this paper, we are discussing basic reversible gates, algorithm of 2x2 vedic multiplier and 4x4 vedic multiplier and how it is optimized by reducing number of

Reversible logic c ircuits have the same number of inputs and outputs, and have one-to-one mapping between vectors of inputs and outputs; thus the vector of

The proposed Full adder can be implemented using combination of all optical reversible NOR logic gate and using all optical reversible NAND gate (NAND logic based

Power demand of the mixer’s drive reveals the mixer’s operating characteristics and reliable monitoring of the mixing processes involving the evaluation of power consumption

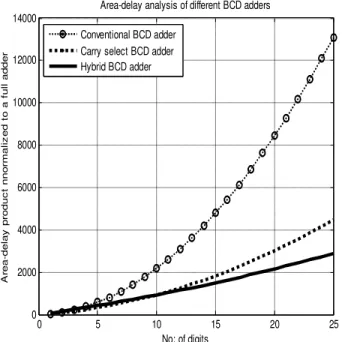

It is clear that the Execution speed of Hybrid signed digit (HSD) adder algorithm increases as the word length of operand increases it is so because it provides the carry-