High speed multiplier design using Decomposition Logic

Texto

Imagem

Documentos relacionados

Reversible logic c ircuits have the same number of inputs and outputs, and have one-to-one mapping between vectors of inputs and outputs; thus the vector of

In this paper design the 4-bit Vedic multiplier using different adder and implementation 8-bit radix-2 FFT algorithm.. The paper is organized as follows: Section II

A fuzzy model for wind speed prediction and power generation in wind parks using spatial correlation.. Missing wind data forecasting with adaptive neuro-fuzzy

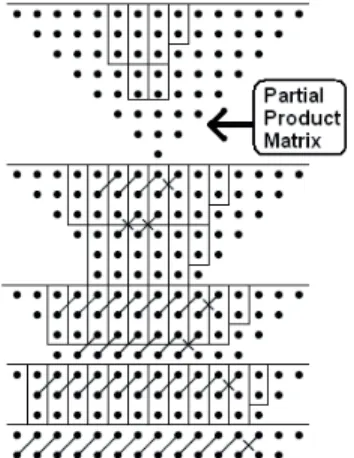

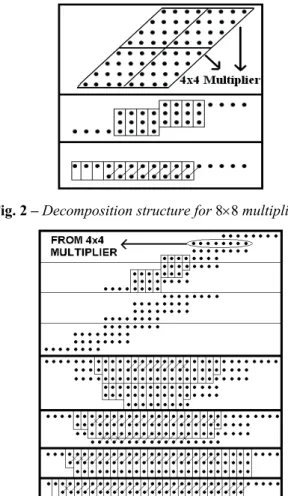

By inserting more number of zeros in the multiplicand using booth recoding unit we can reduce the switching activity by shutting down the idle part of the circuit

Finally all these circuits are compared with their power dissipation, delay and power delay product values, the Type-E circuit connected with Forward Body Bias circuit is shown

Then butterfly operation (BO) is carried out to perform FNT and IFNT where the point wise multiplication is performed using modulo 2n+1 partial product multipliers.. Thus modulo

This approach is used to implement fuzzy logic control based on variable structure technique which is called fuzzy sliding mode controller and applied for controlling the speed of

The multiplier, being the most significant block in many such digital systems, their speed and efficiency are primarily dependent upon the speed, area, throughput