Amplificador Monolítico CMOS para Sinais a 1GHz,

com Ganho Controlado Digitalmente

Fernando Azevedo1,2, Fernando Fortes1,2, M. João Rosário2,3 1

Instituto Superior de Engenharia de Lisboa, Rua Conselheiro Emídio Navarro, 1049-014 Lisboa, Portugal 2

Instituto de Telecomunicações, Av. Rovisco Pais, 1049-001 Lisboa, Portugal 3

Instituto Superior Técnico, Av. Rovisco Pais, 1049-001 Lisboa, Portugal email: fazevedo@deetc.isel.ipl.pt ffortes@deetc.isel.ipl.pt mrosario@alfa.ist.utl.pt

Resumo

Esta comunicação descreve o projecto e simulação de um amplificador monolítico de ganho variável, que pode ser usado na banda ISM (Industrial, Scientific and Medical) dos 900MHz, cujo ganho é controlado directamente por um conjunto de quatro bits. O circuito, totalmente integrado, é implementado numa tecnologia CMOS normalizada

de 0,35µm. As simulações foram obtidas usando o modelo BSIM3 e apresentam um ganho a variar entre um mínimo

de -36dB e um máximo de 28dB a 1GHz e com uma tensão de alimentação de 3V. O consumo total máximo é inferior a 5mW.

Palavras Chave - CMOS RFIC, amplificador de RF, comunicações sem fios, front-end.

I. INTRODUÇÃO

As comunicações sem fios suportam-se em tecnologias que têm vindo a evoluir de uma forma sem precedentes. Com a pressão do mercado dando ênfase à necessidade premente de implementação de circuitos electrónicos cada vez mais complexos, atendendo ao aumento de funcionalidades exigidas, mais leves, de menor custo e consumo reduzido, aumenta a necessidade de pesquisa de soluções inovadoras que permitam uma maior integração dos circuitos electrónicos.

Na cadeia de um front-end para RF, quer na emissão quer na recepção, é necessário adaptar o nível do sinal, por forma a evitar desperdício de potência na emissão ou saturação do sinal na recepção, quando existe um sinal forte na antena. Esta adaptação, normalmente controlada automaticamente, deve ser rápida, minimizando assim distúrbios na frequência (frequency splatter)[1] e optimizando rapidamente as condições de emissão ou recepção no transreceptor. Atendendo à necessidade crescente do nível de integração e eliminação dos componentes discretos em RF, torna-se imperativo que este controlo de ganho seja integrado em conjunto com os restantes blocos do front-end, por forma a atingir o objectivo da integração total.

Esta comunicação descreve o projecto e simulação de um amplificador de sinal monolítico cujo ganho variável é controlado digitalmente por um conjunto de quatro bits. Embora tenha sido projectado para ser usado na banda ISM dos 900MHz, poderá ser facilmente adaptado a outras aplicações. O circuito é constituído por dois blocos de amplificação em cascata (C1 e C2), com entradas e saídas diferenciais, e um módulo DAC, sendo este último o responsável pelo controlo de ganho, conforme se mostra na figura 1. O módulo digital, com quatro bits de entrada, comanda o ganho do amplificador, actuando directamente na

transcondutância dos dispositivos activos. O circuito, totalmente integrado, é implementado numa tecnologia CMOS normalizada de 0,35µm da AMS1

(C35B4)[2], ocupando uma área de sílicio inferior a 0,01mm2.

As simulações foram obtidas usando o modelo BSIM3 e apresentam um ganho a variar entre um mínimo de -36dB e máximo de 28dB, à frequência de 1GHz e com uma tensão de alimentação de 3V. O consumo do circuito, incluindo o bloco digital, é inferior a 5mW.

II. DESCRIÇÃO DO CIRCUITO

Os dois blocos de amplificação são constituídos por dois amplificadores diferenciais clássicos, conforme o circuito apresentado na figura 2. O par diferencial de entrada, constituído pelos dispositivos MX1 e MX2 com largura de gate de 80µm, impõe a transcondutância de entrada. As gates deste par são polarizadas com a tensão VRef, através de MX3 e MX4. O grupo de dispositivos M0X, M1X, M2X e M3X, associados em paralelo, implementam um espelho de corrente activo que polariza este andar amplificador enquanto os dispositivos M0Y, M1Y, M2Y e M3Y implementam o espelho de corrente do par diferencial de saída. Estes dois grupos funcionam como conversores DAC. Cada um dos dispositivos de cada grupo funciona como sub-espelho, sendo a sua corrente ponderada com o peso do bit a ele associado, como será mostrado abaixo. A corrente total do espelho é o somatório dessas correntes.

Uma vantagem deste tipo de controlo é que o circuito responde muito rapidamente a alterações da palavra digital, adaptando-se o ganho às necessidades de utilização.

A partir da figura 3, que representa isoladamente um dos espelhos atrás referido, pode verificar-se que a corrente total aplicada ao par diferencial é dada

pela equação (1),

sendo B0, B1, B2, e B3, o estado lógico (zero/um), de cada um dos bits da entrada digital. Tomando como referência a largura de gate do dispositivo M0, considerando que a largura, W, e comprimento, L, das gates dos dispositivos são atribuídas segundo as relações registadas em (2) e aplicando a equação da corrente de dreno em função da tensão VGS para um dispositivo MOS (3), que contempla o

1

Áustria Micro Systems

RL VGND VDD VRF VO -VO+ Digital Ctl IRef1 VC1 C1 VI+ V I-IRef VO+ V O-V BI AS+ I Re f1 C2 VI+ V I-IRef VO+ V O-RL RL RL VB3 VB2 VB1 VB0 V BI AS-I Re f2

Figura 1. Diagrama de blocos.

M3XM3Y IRef VO+ M2XM2Y M1XM1Y M0XM0Y MRef VB2 VB1 VB0 VB3 MX1 MX2 MY1 MY2 RL RL RL RL MX4 MX3 VRef VDD VRF V O-C1 VGND

Figura 2. Circuito amplificador e controlo.

) 1 ( 0 0 1 1 2 2 3 3 B I B I B I B I IS = D ⋅ + D ⋅ + D ⋅ + D ⋅

estado do bit respectivo,

vem para a corrente total IS, igual em ambos os espelhos de corrente,

Esta corrente impõe a transcondutância dinâmica, como demonstra a equação (5), de ambos os dispositivos de cada um dos pares diferenciais, permitindo assim modificar o ganho dos mesmos de acordo com o peso da palavra binária B3B2B1B0. Como W0Y=W0X, W1Y=W1X, W2Y=W2X, W3Y=W3X as correntes de polarização fornecidas pelos dois espelhos são iguais mas, devido a terem largura de gate superior, a transcondutância dinâmica do par diferencial de entrada é superior ao de saída, como comprova a equação.

As larguras de gate dos dispositivos de ambos os pares diferenciais, assim como a largura dos dispositivos tomados como referência para o controlo da corrente de polarização dos mesmos pares, foram optimizadas para um ganho elevado, mas sem comprometer a banda de frequência de operação. Assim, WX2=WX1=80µm para o par de entrada, WY2=WY1=20µm para o par de saída e W0Y=W0X=5µm para o par referência.

Todo o circuito é constituído somente por dispositivos MOS de canal-n e cargas resistivas aplicadas na saída dos pares diferenciais. As cargas são resistivas, em vez de activas, por duas razões: a utilização de dispositivos activos p-MOS conduz a grandes áreas capacitivas que atenuam o sinal. Circuitos activos com cargas resistivas permitem operar com frequências mais elevadas; em segundo lugar, a saída do primeiro par tem que simultaneamente adaptar-se e ser fonte de polarização da entrada do par seguinte, atendendo a que é usado acoplamento directo.

O circuito apresentado não necessita de qualquer indutância e não existe necessidade de qualquer sintonia, a não ser que seja usado antes do LNA, junto à antena, sendo necessário nesse caso fazer a devida adaptação à entrada.

A entrada do amplificador foi propositadamente transformada em não-diferencial para que este possa ser testado experimentalmente com um gerador de RF convencional. A passagem de quatro para um número superior de bits, por forma a aumentar a resolução do DAC, não apresenta grande dificuldade, exigindo no entanto alguma atenção na atribuição das dimensões dos MOS, por forma a garantir as relações referidas em (2) e o compromisso entre capacidade parasita dos dispositivos e transcondutância dinâmica dos mesmos.

M3 MRef M2 M1 M0 23.W0 20.W0 22.W0 22.W0 IRef VB3 + -4.W0 n 3 0 n n D S I B I =

∑

⋅ = VB2 + - VB0 + -VB1 + -3 D3B I ⋅ ID2⋅B2 ID1⋅B1 ID0⋅B0Figura 3. Funcionamento do espelho de corrente. (3) B Vt) (V L W K 2 1 I 2 n GS n n Dn = ⋅′ − ⋅

[

2 B 2 B 2 B 2 B]

(4) 4 I I Ref 3 3 2 2 1 1 0 0 S= ⋅ ⋅ + ⋅ + ⋅ + ⋅ 0 0 0 0 1 1 0 2 2 0 3 3 0 1 2 3 Ref W 2 W W 2 W (2) W 2 W W 2 W L L L L L ⋅ = ⋅ = ⋅ = ⋅ = = = = =[

2 B 2 B 2 B 2 B]

(5) 2 I L W K g 0 0 1 1 2 2 3 3 Ref m = ⋅′ ⋅ ⋅ ⋅ + ⋅ + ⋅ + ⋅O layout, apresentado na figura 7, foi cuidadosamente desenhado por forma a evitar assimetrias e grandes áreas capacitivas, pelas razões apontadas atrás.

IV. SIMULAÇÕES

As simulações do circuito mostram resultados prometedores no que respeita ao controlo do ganho e consumo de potência (PDD). O circuito foi simulado em várias condições de funcionamento sendo que os resultados apresentados foram obtidos com uma fonte de alimentação de 3V e uma frequência fRF=1GHz. Com tensão de entrada de RF de -40dBV o ganho foi optimizado, ajustando a corrente de polarização Iref. Alcançados os valores óptimos, os resultados simulados são os apresentados nas figuras 4, 5 e 6 e tabela I.

A figura 4 apresenta a curva de ganho de tensão e consumo de corrente total do circuito em função do nível da palavra digital, negada, de quatro bits. Verifica-se que a variação do ganho se situa entre -36dB e +28dB e que o consumo de corrente varia entre 200µA e 1,7mA.

Relativamente à curva de ganho, esta apresenta uma evolução não linear, devido à representação em escala logarítmica. Quanto à curva de consumo de corrente total, verifica-se uma boa linearidade comprovando que o DAC apresenta incrementos iguais em toda a gama binária.

A figura 5 apresenta curvas de tensão de sinal de saída em função da amplitude do sinal de entrada para duas situações distintas da palavra binária de controlo: W=0000 (ganho máximo) e W=1111 (ganho mínimo). Desta figura obtém-se o ponto de compressão a 1dB na entrada que é de -17dBV quando o ganho é máximo. Pode verificar-se que, antes de iniciar a compressão, o amplificador apresenta uma boa linearidade nas duas situações.

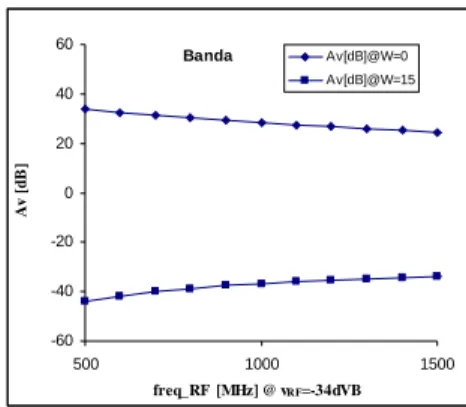

A figura 6 apresenta curvas de ganho de tensão em função de frequência na banda [500;1500]MHz, para as mesmas situações da palavra binária de controlo registadas na figura anterior. Verifica-se que o ganho diminui ligeiramente com a frequência na situação em que é máximo (W=0000) e aumenta quando é mínimo (W=1111). Isto acontece devido ao compromisso entre a capacidade parasita dos dispositivos e a transcondutância dinâmica dos mesmos, pois os dois evoluem de forma oposta.

-40 -30 -20 -10 0 10 20 30 0 2 4 6 8 10 12 14 16 W=f(B3,B2,B1,B0) Av [ d B ] 0 0,5 1 1,5 2 I To t [m A] Ga nho [ dB] ITot [ mA] vRF=-34dB V @1GHz

Figura 4. Ganho de tensão e consumo de corrente total. Ponto de Compressão -120 -100 -80 -60 -40 -20 0 20 40 -80 -60 -40 -20 0 20 VRF [dBV]@1GHz V o 1 , V o2 [d B V ] Vo[dBV]@W=0 Vo[dBV]@W=15

A simulação com uma corrente IRef=200µA impôs ISY=ISX=740µA, que está de acordo com a equação 4 na condição de todos os bits activos, vindo para a corrente total 1,68mA.

V. CONCLUSÕES

Esta comunicação apresenta um amplificador monolítico cujo ganho é controlado digitalmente por um conjunto de quatro bits. O circuito total, amplificador e controlo digital, é completamente integrado (figura 7) numa tecnologia normalizada CMOS de baixo custo e encontra-se presentemente em fase de fabrico. Ocupa uma área de silício de 500µmX500µm, incluindo bond-pads, permitindo a integração futura de um front-end completo para comunicações sem fios. As simulações demonstram que quando o circuito é alimentado a 3V e com um sinal de 1GHz o amplificador tem um ganho mínimo de -36dB e máximo de 28dB. Na situação de ganho máximo, a corrente DC total é de 1,67mA.

Tabela I – Características do amplificador

Tecnologia de Silício: CMOS 0,35µm (AMS) Área útil do circuito: 0,015mm2

Área total (incluindo pads): 0,25mm2 Tensão de alimentação: 3V Corrente total máxima: 1,7mA

Frequência de RF: 1000MHz Ganho máximo @1GHz: 28dB

Ganho mínimo @1GHz -36dB Níveis de controlo 16

Ponto de comp. a 1dB na entrada: -17dBV

VI. R

EFERÊNCIAS[1] A. Rofougaran et al., "A Single-Chip 900MHz Spread-Spectrum Wireless Transceiver in 1µm CMOS,"

IEEE Journal of Solid-State Circuits., vol. 33-4,pp. 515-534, April 1998.

[2] AMS−Austria Mikro Systems International AG, "0.6µm CMOS Design Rules", 1997.

Banda -60 -40 -20 0 20 40 60 500 1000 1500 freq_RF [MHz] @ vRF=-34dVB Av [ d B ] Av[dB]@W=0 Av[dB]@W=15

Figura 6. Ganho de tensão em função da frequência.

![Figura 4. Ganho de tensão e consumo de corrente total. Ponto de Compressão -120-100 -80-60-40-2002040 -80 -60 -40 -20 0 20 V RF [dBV]@1GHzVo1, Vo2 [dBV]Vo[dBV]@W=0Vo[dBV]@W=15](https://thumb-eu.123doks.com/thumbv2/123dok_br/15964275.1100044/4.918.514.789.441.686/figura-ganho-tensão-consumo-corrente-ponto-compressão-ghzvo.webp)