OPERAÇÃO ANALÓGICA DE TRANSISTORES DE MÚLTIPLAS PORTAS

EM FUNÇÃO DA TEMPERATURA

RODRIGO TREVISOLI DORIA

OPERAÇÃO ANALÓGICA DE TRANSISTORES DE MÚLTIPLAS PORTAS EM FUNÇÃO DA TEMPERATURA

Tese apresentada à Escola Politécnica da Universidade de São Paulo para a obtenção do título de Doutor em Engenharia Elétrica.

Área de Concentração: Microeletrônica

Orientador: Prof. Dr. Marcelo Antonio Pavanello

AGRADECIMENTOS

Ao meu orientador, professor Dr. Marcelo Antonio Pavanello, que sempre recebeu com entusiasmo todos os resultados alcançados, agradeço pela confiança depositada e por todos os ensinamentos, tão importantes durante este trabalho.

Ao prof. Dr. Jean-Pierre Colinge por ter me recebido em seu grupo de pesquisa e disponibilizado toda a infra-estrutura do Tyndall National Institute, Irlanda, possibilitando

que eu estudasse um dos dispositivos mais inovadores do momento.

Aos meus pais Francisco e Sonali que, por mim, foram à Irlanda e, se necessário fosse, iriam a Marte e ao meu irmão Renan, que espero, algum dia, poder recompensar pela grande contribuição através de idéias e discussões técnicas.

À amiga Michelly de Souza, agora professora e doutora, que procurou sanar minhas dúvidas sempre que necessário.

Ao prof. Dr. João Antonio Martino, por me dar a oportunidade de integrar o grupo de pesquisa SOI-CMOS e a todos os meus companheiros de grupo.

Aos meus avós Adão e Anna que sempre me incentivaram e estiveram ao meu lado, torcendo por mim, durante toda a minha vida.

Ao Centro Universitário da FEI, por toda a infra-estrutura disponibilizada durante meus anos de mestrado e doutorado e a todos os amigos que lá consegui.

À FAPESP, pelo suporte financeiro prestado ao longo dos últimos três anos, tornando possível a conclusão do doutorado.

RESUMO

Neste trabalho, é apresentada uma análise da operação analógica de transistores de múltiplas portas, avaliando a tensão Early, o ganho de tensão em malha aberta, a razão da transcondutância pela corrente de dreno (gm/IDS), a condutância de

dreno e, em especial, a distorção harmônica, exibida por estes dispositivos. Ao longo deste trabalho, foram estudados FinFETs, dispositivos de porta circundante ( Gate-All-Around – GAA) com estrutura de canal gradual (Graded-Channel – GC) e transistores

MOS sem junções (Junctionless - JL). Inicialmente, foi efetuada a análise da distorção

harmônica apresentada por FinFETs com e sem a presença de tensão mecânica biaxial, com diversas larguras de fin (Wfin) e comprimentos de canal (L), quando estes

operavam em saturação, como amplificadores de um único transistor. Nesta análise, as não-linearidades foram avaliadas através da extração das distorções harmônicas de segunda e terceira ordens (HD2 e HD3, respectivamente), mostrando que a presença de tensão mecânica tem pouca influência em HD2, mas altera levemente a HD3. Quando os ganhos de tensão em malha aberta dos dispositivos são levados em conta, transistores sem tensão, também chamados de convencionais, mais estreitos apresentam grande vantagem em termos de HD2 em relação aos tensionados. Ainda nesta análise, percebeu-se que HD2 e HD3 de transistores tensionados pioram com a redução da temperatura, especialmente em inversão mais forte. Na seqüência, foi efetuada uma análise de HD3 em FinFETs com e sem tensão mecânica de vários comprimentos e larguras de canal, operando em região triodo e aplicados a estruturas balanceadas 2-MOS, mostrando que presença de tensão mecânica traz pouca influência em HD3, mas reduz a resistência do canal dos dispositivos (RON), o que não é

bom em estruturas resistivas, como as avaliadas. Nesta análise, ainda, pode-se perceber uma melhora em HD3 superior a 30 dB ao se incrementar VGT de zero a 1,0 V,

vantagem em HD3 em relação aos demais, para valores de VGT superiores a 2 V. Na

avaliação destas estruturas em função da temperatura, percebeu-se que, para VGT

superiores a 1,1 V, HD3 depende fortemente da temperatura e piora conforme a temperatura diminui. O estudo envolvendo transistores sem junções foi mais focado em seus parâmetros analógicos, comparando-os aos apresentados por dispositivos de porta tripla ou FinFETs. Em inversões moderada e forte, transistores sem junção apresentaram menores valores para gm/IDS em relação a dispositivos de FinFETs

polarizados em um mesmo nível de corrente, entretanto, a dependência de gm/IDS com a

temperatura em transistores sem junção também foi menor que a apresentada por FinFETs. JL e FinFETs apresentaram comportamentos distintos para a tensão Early e o ganho de tensão em malha aberta em função da temperatura. Estes parâmetros sempre melhoram com o aumento da temperatura em dispositivos JL, enquanto que exibem seu máximo valor em temperatura ambiente em FinFETs. Nas proximidades da tensão de limiar, transistores sem junção com largura de fin de 30 nm exibiram tensão Early e ganho superiores a 80 V a 57 dB, respectivamente, enquanto que FinFETs mostraram Tensão Early de 35 V e ganho de 50 dB. Em todos os estudos efetuados ao longo do trabalho, procurou-se apontar as causas das não-linearidades apresentadas pelos dispositivos, a partir de modelos analíticos que pudessem relacionar a física de funcionamento dos transistores com os resultados experimentalmente obtidos.

ABSTRACT

In this work it is presented an analysis of the analog operation of multiple gate transistors, evaluating the Early Voltage, the open-loop voltage gain, the transconductance over the drain current ratio (gm/IDS), the drain conductance and,

especially, the harmonic distortion exhibited by these devices. Along the work, FinFETs, Gate-All-Around (GAA) devices with the Graded-Channel (GC) structure and MOS transistors without junctions (Junctionless - JL) were studied. Initially, an analysis of the harmonic distortion presented by conventional and biaxially strained FinFETs with several fin widths (Wfin) and channel lengths (L) was performed, when these devices

were operating in saturation as single transistor amplifiers. In this analysis, the non-linearities were evaluated through the extraction of the second and the third order harmonic distortions (HD2 and HD3, respectively), and it was shown that the presence of strain has negligible influence in HD2, but slightly changes HD3. When the open loop voltage gain of the devices is taken into consideration, narrower conventional transistors present a huge advantage with respect to the strained ones in terms of HD2. Also, it was perceived that both HD2 and HD3 of strained FinFETs worsen with the temperature decrease, especially in stronger inversion. In the sequence, an analysis of the HD3 presented by conventional and strained FinFETs of several fin widths and channel

lengths operating in the triode regime was performed. These devices were applied to 2-MOS balanced structures, showing that the presence of the strain does not influence significantly the HD3, but reduces the resistance in the channel of the transistors (RON),

which is not good for resistive structures as the ones evaluated. In this analysis, it can also be observed an HD3 improvement of 30 dB when VGT is increased from zero up to

1,0 V, where narrower devices present transfer characteristics more linear than the wider ones. Then, it was studied the distortion presented by GAA and GC GAA devices operating in the triode regime, applied to 2-MOS structures. In this case, it could be perceived that GC GAAs with longer lightly doped regions present better HD3 in comparison to the other devices for VGT higher than 2.0 V. In the evaluation of these

1.1 V, HD3 strongly depends on the temperature and worsens as the temperature decreases. The study involving JL transistors was focused on their analog parameters, comparing them to the ones presented by triple gate devices or FinFETs. In moderate and strong inversions, Junctionless showed lower values for gm/IDS with respect to triple

gate devices biased at a similar current level. However, the dependence of gm/IDS from

Junctionless with the temperature was also smaller than the one presented by FinFETs. Junctionless and FinFETs exhibited distinct behaviors for the Early voltage and the open-loop voltage gain as a function of the temperature. These parameters always improve with the temperature raise in JL devices whereas they exhibit their maximum values around room temperatures for FinFETs. In the proximity of the threshold voltage, Junctionless with fin width of 30 nm presented Early voltage and intrinsic gain larger than 80 V and 57 dB, respectively, whereas FinFETs exhibited Early voltage of 35 V and gain of 50 dB. For all the studies performed in this work, the probable causes of the non-linearities were pointed out, from analytic models that could correlate the physical work of the devices with the experimental results.

LISTA DE FIGURAS

Figura 2.1 – Estruturas de transistores de porta dupla: (A) FinFET e (B) MOSFET DELTA. ... 37 Figura 2.2 – Esquema da inversão de volume em um MOSFET de porta dupla com filme

fino em (A) VGS ≤ VTH e em (B) VGS > VTH 6. ... 38

Figura 2.3 – Estrutura multi-dedos ou multi-fins. ... 39

Figura 2.4 – Estrutura final do dispositivo Gate-All-Around em (A) perspectiva e (B) corte

transversal. ... 42 Figura 2.5 – Corte transversal do dispositivo de porta circundante com arquitetura de

canal gradual (GC GAA)... 44 Figura 2.6 – (A) Esquema tridimensional de um transistor de múltiplas portas, (B) corte

transversal do dispositivo nMOS sem junções e (C) secção transversal de um nMOS FinFET ou Trigate modo inversão. ... 46 Figura 2.7 – Esquema da geração da distorção harmônica em um transistor MOS. ... 48 Figura 2.8 – Normalização da característica corrente-tensão através do IFM. ... 56 Figura 2.9 – Característica de transferência normalizada nos eixos x e y, onde são

evidenciadas as áreas abaixo e acima da curva. ... 57 Figura 2.10 – Diferença da saída normalizada menos o sinal de entrada, yr(x)-x, e seu

módulo |yr(x)-x| 67. ... 59 Figura 2.11 – Bloco amplificador formado por um único transistor MOS. ... 62 Figura 2.12 – Definição da tensão Early a partir da característica IDS vs. VDS de um

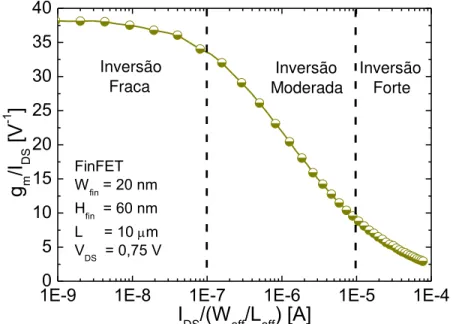

transistor MOS. ... 63 Figura 2.13 – Esboço da curva de gm/IDS em função de IDS/(Weff/Leff) para um FinFET de

Wfin = 20 nm e L = 10 m 75. ... 65

Figura 2.17 – Efeitos da variação da temperatura na concentração intrínseca de portadores e na largura de banda proibida... 74 Figura 2.18 – Efeitos da variação da temperatura na porcentagem de impurezas

ionizadas e no potencial de Fermi. ... 76 Figura 3.1 – Curvas experimentais de IDS/W vs. VGT com VDS = 0,75 V para dispositivos

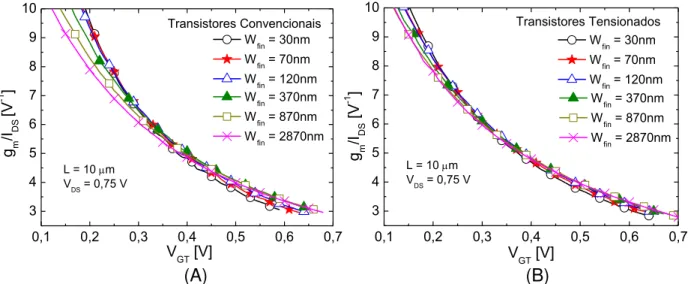

(A) convencionais e (B) tensionados de L = 10 µm. ... 87 Figura 3.2 – Curvas de gm/IDS vs. VGT para dispositivos (A) convencionais e (B)

tensionados polarizados com VDS = 0,75 V de L = 10 µm e diversos Wfin. ... 88

Figura 3.3 – Curvas de AV vs. gm/IDS para (A) dispositivos convencionais e (B)

transistores com tensão mecânica com VDS = 0,75 V para diversos Wfin e L = 10 µm.

... 89 Figura 3.4 – Curvas de HD2 vs. gm/IDS para dispositivos (A) convencionais e (B)

tensionados com L = 10 m, Va = 50 mV e diversos Wfin em VDS = 0,75 V calculadas

através do IFM e de (2.21). ... 92 Figura 3.5 – Curvas de gm/W e (dgm/dVGT)/W em função de gm/IDS para transistores (A)

convencionais e (B) tensionados de L = 10 m e diversos Wfin com VDS = 0,75 V. .. 93

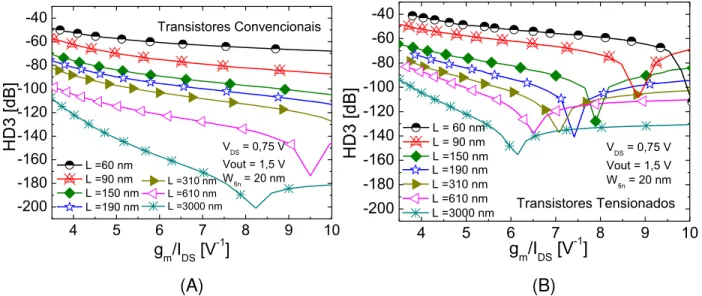

Figura 3.6 – Curvas de HD3 vs. gm/IDS obtidas para (A) dispositivos convencionais e (B)

transistores com tensão mecânica com VDS = 0,75 V e Va = 50 mV para diversos

Wfin e L = 10 µm calculadas através do IFM e de (2.22). ... 96

Figura 3.7 – Curvas de HD3 vs. gm/IDS para dispositivos FinFETs convencionais

simuladas no Atlas 111 com L = 910 nm e três W

fin diferentes, polarizadas em

VDS = 0,75 V e Va = 50 mV. ... 100

Figura 3.8 – HD2 vs. gm/IDS extraído para (A) dispositivos convencionais e (B)

transistores com tensão mecânica com VDS = 0,75 V e Vout = 1,5 V para diversos

Wfin. ... 103

Figura 3.9 – HD3 vs. gm/IDS extraído para (A) dispositivos convencionais e (B)

transistores com tensão mecânica com VDS = 0,75 V e Vout = 1,5 V para diversos

Wfin. ... 104

Figura 3.10 – Curvas medidas de HD2 vs. gm/IDS obtidas para (A) dispositivos

convencionais e (B) com tensão mecânica com VDS = 0,75 V e Vout = 1,5 V para

Figura 3.11 – Curvas medidas de HD3 vs. gm/IDS obtidas para (A) dispositivos

convencionais e (B) transistores com tensão mecânica com VDS = 0,75 V e

Vout = 1,5 V para diversos L e Wfin = 20 nm. ... 106

Figura 3.12 – Curvas medidas de HD3/AV vs. gm/IDS obtidas para (A) dispositivos

convencionais e (B) transistores com tensão mecânica com VDS = 0,75 V e

Va = 50 mV para diversos L e Wfin = 20 nm. ... 107

Figura 3.13 – Curvas experimentais da corrente de dreno em função de VGT para

dispositivos com tensão mecânica com VDS = 0,75 V para diversas temperaturas.

... 108 Figura 3.14 – Curvas medidas de HD2 e HD3 em função de gm/IDS para transistores

com tensão mecânica com VDS = 0,75 V e Va = 50 mV em diversas temperaturas

(L = 10 µm e Wfin = 30 nm). ... 109

Figura 3.15 – Características experimentais de HD2 e HD3 vs. T obtidas para

transistores com tensão mecânica com VDS = 0,75 V e Va = 50 mV para diversos

Wfin. ... 111

Figura 3.16 – AV vs. T extraído para dispositivos com tensão mecânica com

VDS = 0,75 V e VGT = 0,2 V para Wfin de 30 nm e 570 nm. ... 112

Figura 3.17 – Esquema da estrutura balanceada com 2 transistores (2-MOS). ... 115 Figura 3.18 – Curvas da corrente de dreno para dois FinFETs convencionais (IDS1 e IDS2)

com L = 10 µm e Wfin = 30 nm e a corrente total na fonte comum (IDSt = IDS1 – IDS2)

da estrutura 2-MOS em função de VDS com VGT = 0,5 V. ... 116

Figura 3.19 – Curvas de HD3 em função de VGT extraídas para estruturas balanceadas

com FinFETs com diversos Wfin de L = 10 m e Va de (A) 0,1 V e (B) 0,25 V. ... 117

Figura 3.20 – Curvas de HD3 em função de Va extraídas experimentalmente para estruturas balanceadas compostas por dispositivos FinFETs de diversos Wfin,

L = 10 m e VGT = 1,0 V. ... 118

Figura 3.21 – Curvas de HD3, HD5 e THD em função de VGT extraídas para estruturas

balanceadas com FinFETs de L = 10 m, Wfin = 70 nm e Va de 0,25 V. ... 119

Figura 3.22 – HD3 vs. Wfin extraído para estruturas 2-MOS com FinFETs de 10 m de

Figura 3.23 – Curvas de HD3 em função de VGT calculadas a partir da expressão (3.11)

para estruturas balanceadas composta por FinFETs de diversos Wfin, L = 10 m e

Va = 0,1 V. ... 122 Figura 3.24 – Curvas de eff/W vs. VGT extraídas para estruturas balanceadas 2-MOS

com FinFETs de diversos Wfin, L = 10 m e Va = 0,25 V. ... 123

Figura 3.25 – Curvas de HD3 vs. VGT extraídas para estruturas 2-MOS compostas por

FinFETs convencionais e tensionados de diversos Wfin com L = 10 m e Va= 0,15 V.

... 125 Figura 3.26 – HD3 vs. Wfin extraído para estruturas 2-MOS compostas por FinFETs

convencionais e com tensão mecânica de L = 10 m e Va = 0,15 V... 126 Figura 3.27 – Curvas de HD3 vs. VGT para estruturas balanceadas 2-MOS com FinFETs

convencionais e tensionados com Wfin = 20 nm e diversos comprimentos de canal.

... 127 Figura 3.28 – HD3 vs. RON.W extraído para estruturas balanceadas compostas por

FinFETs (A) convencionais e (B) tensionados de diversos Wfin com L = 10 m

polarizados em Va = 0,15 V. ... 128 Figura 3.29 – Curvas de HD3 vs. L para estruturas balanceadas 2-MOS compostas por

FinFETs convencionais e tensionados com Wfin = 20 nm polarizados em

Va = 0,15 V. ... 129 Figura 3.30 – Curvas (A) IDS vs. VGT e (B) gm vs. VGT simuladas e experimentais com

VDS = 1,5 V para dispositivos GC GAA com L = 3 m em T = 300 K. ... 132

Figura 3.31 – Curvas de (A) THD e (B) HD3 experimentais e simuladas em função da amplitude de entrada para dispositivos GC GAA. ... 133 Figura 3.32 – Curvas simuladas de HD3 em função de VGT para estruturas 2-MOS

formadas por dispositivos GAA convencional e GC GAA com (A) Va = 0,25 V e (B) Va = 0,50 V. ... 135 Figura 3.33 – Curvas simuladas de HD3 vs. Va para estruturas 2-MOS compostas por

dispositivos GAA convencionais e GC GAA de diferentes razões LLD/L com (A)

VGT = 2,1 V e (B) RON = 20 k 2%. ... 136

Figura 3.34 – Curvas simuladas de gm em função de VGT para GAAs convencionais e

Figura 3.35 – Curvas da corrente IDS em função da tensão aplicada a uma das entradas

VDS da estrutura 2-MOS formada com transistores GAA convencional para diversas

temperaturas. ... 141 Figura 3.36 – Curvas de HD3 vs. VGT simuladas para dispositivos GAA convencionais e

GC GAAs de diversos LLD/L com temperaturas entre 100 K e 300 K. ... 142

Figura 3.37 – Curvas experimentais de IDS vs. VGT com VDS = 1,0 V para dispositivos JL

e FinFETs de modo inversão (IM) de diversos Wfin,mask e L = 1,0 µm... 146

Figura 3.38 – (A) gm/IDS vs. IDS/(W/L) e (B) IDSvs. VGT para dispositivos JL e FinFETs de

modo inversão (IM) de diversos Wfin,mask e L = 1,0 µm com VDS = 1,0 V. ... 147

Figura 3.39 – Curvas de VEA vs. gm/IDS extraídas para JL e FinFETs de modo inversão

para transistores de diferentes Wfin,mask e L = 1,0 µm com VDS = 1,0 V. ... 148

Figura 3.40 – AV vs. gm/IDS obtido para JL e FinFETs de modo inversão com VDS = 1,0 V

para transistores de diferentes Wfin,mask e L = 1 µm. ... 149

Figura 3.41 – Curvas de gm e gD em função de gm/IDS simuladas 154 e experimentais

para dispositivos JL e FinFETs de modo inversão de L = 1,0 µm com VDS = 1,0 V.

... 152 Figura 3.42 – Curvas de gD vs. VDS simuladas 154 para dispositivos JL e FinFETs de

modo inversão de L = 1,0 µm com VDS = 1,0 V considerando µ0 similar em ambos os

dispositivos. ... 153 Figura 3.43 – (A) N(x) e (B) N(x)/VDS na direção do comprimento de canal (x) obtidos

através das estruturas simuladas de JL e FinFETs modo inversão 154 de L = 1,0 µm,

Wfin,sim = 10 nm e Hfin = 10 nm em diferentes VGT. ... 154

Figura 3.44 – (A) Campo elétrico e (B) Eeff(x)/VDS na direção do comprimento de canal

obtidos através das estruturas simuladas de JL e FinFETs modo inversão 154 de L = 1,0 µm, Wfin,sim = 10 nm e Hfin = 10 nm em diferentes VGT. ... 155

Figura 3.45 – Curvas de IDS vs. VGS para dispositivos (A) FinFETs e (B) JL de

L = 1,0 µm e Wfin,mask = 30 nm com VDS = 1,0 V e diversas temperaturas e curvas IDS vs. VGT para transistores (C) FinFETs e (D) JL em similar polarização e

Figura 3.46 – Características (A) gm/IDS vs. IDS/(W/L) e (B) gm/IDS vs. VGT para

dispositivos JL e FinFETs de L = 1,0 µm e Wfin,mask = 30 nm com VDS = 1,0 V e

temperaturas entre 223 K e 473 K. ... 159 Figura 3.47 – Curvas de gm/IDS vs. IDS/(W/L) para transistores JL de L = 1,0 µm e

Wfin,mask = 30 nm com VDS = 1,0 V e temperaturas entre 100 K e 380 K. ... 160

Figura 3.48 – Tensão Early em função de gm/IDS extraída para dispositivos JL e FinFETs

de modo inversão de (A) Wfin,mask = 30 nm e (B) Wfin,mask = 40 nm com L = 1,0 µm,

VDS = 1,0 V e temperaturas entre 223 K e 473 K. ... 161

Figura 3.49 – VEA vs. T experimentais para dispositivos JL e FinFETs de diversos Wfin e

ND com VDS = 1,0 V e VGT = 0,4 V. ... 162

Figura 3.50 – Curvas de (A) AVvs. T e (B) AV vs. gm/IDS extraídas para dispositivos JL e

FinFETs de L = 1,0 µm com VDS = 1,0 V. ... 163

Figura 3.51 – (A) HD2 vs. gm/IDS e (B) HD3 vs. gm/IDS extraídas para dispositivos JL e

FinFETs de modo inversão com Va = 50 mV, VDS = 1,0 V e temperaturas entre

223 K e 473 K. ... 165 Figura 3.52 – (A) HD2 vs. gm/IDS e (B) HD3 vs. gm/IDS extraídas para dispositivos JL e

FinFETs de modo inversão com Vout = 1,5 V, VDS = 1,0 V e temperaturas entre

LISTA DE TABELAS

Tabela 3.1 – Resistência série (RS.W) calculada para FinFETs com e sem a presença

de tensão mecânica e diversas larguras de fin (Wfin). ... 87

Tabela 3.2 – Mobilidade de baixo campo (µ0) e coeficiente de degradação da

mobilidade (θ) calculado para FinFETs com e sem a presença de tensão mecânica e diversas larguras de fin (Wfin). ... 95

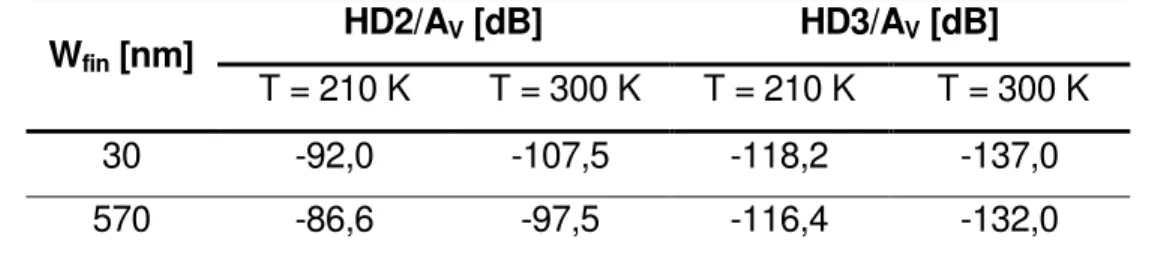

Tabela 3.3 – Comparação entre HD2/AV e HD3/AV de ambos os dispositivos de

Wfin = 30 nm e 570 nm em gm/IDS = 5 V-1 para diferentes temperaturas. ... 112

Tabela 3.4 – Coeficiente de degradação da mobilidade (θ2) calculado para FinFETs

medidos experimentalmente com L = 10 m e diversos Wfin. ... 121

LISTA DE SÍMBOLOS

s Constante de espalhamento (cm/V)

Parâmetro de ajuste do modelo de Lombardi para a rugosidade de superfície (V/s)

side Parâmetro de ajuste do modelo de Lombardi para a rugosidade de

superfície nas laterais do FinFET (V/s)

top Parâmetro de ajuste do modelo de Lombardi para a rugosidade de

superfície no topo do FinFET (V/s)

ox Permissividade do óxido (F/cm)

Si Permissividade do silício (F/cm)

Ângulo de defasagem da função de entrada do dispositivo na análise por Taylor

B Potencial de superfície aproximado para a inversão forte (V)

F Potencial de Fermi (V)

S Potencial de superfície (V)

Constante de efeito de corpo (V1/2)

Comprimento de canal natural (cm)

b Mobilidade do substrato (cm2/V.s)

eff Mobilidade efetiva (cm2/V.s)

0 Mobilidade de baixo campo (cm2/V.s)

ph Espalhamento por fônons acústicos (cm2/V.s)

sr Espalhamento por rugosidade da superfície (cm2/V.s)

Fator de degradação da mobilidade no modelo linear (V-1)

1 Fator de degradação da mobilidade no modelo quadrático (V-1)

2 Fator de degradação da mobilidade no modelo quadrático (V-2)

Freqüência angular do sinal de entrada (Hz)

a0 Amplitude do nível DC para a série de Fourier

an Amplitude do enésimo termo da série de Fourier em função do cosseno

de

A Amplitude da função aplicada na entrada do dispositivo AREA1 Área acima da curva normalizada para a aplicação do IFM AREA2 Área abaixo da curva normalizada para a aplicação do IFM AV Ganho de tensão em malha aberta para baixas freqüências

B Parâmetro de ajuste do modelo de Lombardi para o espalhamento de fônons (cm2/V.s)

bn Amplitude do enésimo termo da série de Fourier em função do seno de

C Capacitor presente nos integradores de circuitos 2-MOS (F)

C’ Parâmetro de ajuste do modelo de Lombardi para o espalhamento de fônons (cm2/V.s)

C0 Coeficiente de Fourier correspondente à amplitude do nível DC do sinal

de saída

C1 Coeficiente de Fourier correspondente à amplitude do sinal de

freqüência fundamental na saída

C2 Coeficiente de Fourier correspondente à amplitude do segundo

harmônico no sinal de saída

CL Carga capacitiva de um circuito amplificador (F)

Cn Coeficiente de Fourier correspondente à amplitude do harmônico de

ordem n no sinal de saída

Cox Capacitância do óxido de porta por unidade de área (F/cm2)

CS Capacitância do silício por unidade de área (F/cm2)

D Primeira função integral para o cálculo da distorção harmônica Dr Terceira função integral para o cálculo da distorção harmônica Drs Quarta função integral para o cálculo da distorção harmônica Ds Segunda função integral para o cálculo da distorção harmônica E Campo elétrico vertical (V/cm)

Eeff Campo elétrico efetivo (V/cm)

EFp Nível de Fermi para as lacunas (eV)

Eg Largura de banda proibida (eV) Esat Campo elétrico de saturação (V/cm) f Freqüência do sinal de entrada (Hz)

fT Freqüência de ganho unitário (Hz)

fC Freqüência de corte (Hz)

G Transadmitância de um circuito constituído por transistores MOS (-1)

gD Condutância de dreno (Ω-1)

gm Transcondutância (Ω-1)

ħ Constante de Plank normalizada (1,055 x 10-34 J.s)

HD0 Distorção harmônica referente à parcela DC do sinal de entrada (dB) HD2 Distorção harmônica referente ao harmônico de segunda ordem (dB) HD3 Distorção harmônica referente ao harmônico de terceira ordem (dB) HDn Distorção harmônica referente ao harmônico de enésima ordem (dB)

Hfin Altura do fin do dispositivo (nm)

I Corrente que flui através de um semicondutor (A)

I01 Corrente no nó da entrada negativa do amplificador operacional na

análise de estruturas balanceadas (A)

I02 Corrente no nó da entrada positiva do amplificador operacional na

análise de estruturas balanceadas (A)

Ib Corrente de alimentação do circuito amplificador unitário (A)

IDmulti Corrente de dreno da estrutura multi-fins (A)

ID0 Corrente de um transistor planar de porta simples (A)

IDS Corrente de dreno (A)

IDS1 Corrente de dreno no primeiro transistor das estruturas 2-MOS (A)

IDS2 Corrente de dreno no segundo transistor das estruturas 2-MOS (A)

IDSt Corrente total da estrutura 2-MOS (A)

Iout Corrente de saída de um circuito formado por dispositivos MOS (A)

k Constante de Boltzmann (1,38 x 10-23 J/K)

K1 Coeficiente de Taylor do harmônico fundamental

K2 Coeficiente do segundo harmônico na análise por Taylor

Klow Parâmetro da transcondutância para baixo campo (A/V2)

Kn Coeficiente do enésimo harmônico na análise por Taylor

L Comprimento de máscara do canal do dispositivo ( m) Leff Comprimento efetivo do canal do dispositivo ( m)

LLD Comprimento da região fracamente dopada do canal do dispositivo GC

SOI ( m)

m* Massa de confinamento dos portadores na direção transversal (kg). N Concentração total de dopantes (cm-3)

NA Concentração de dopantes aceitadores (cm-3)

NA- Concentração de impurezas aceitadores ionizadas (cm-3)

NAB Concentração de dopantes no substrato (cm-3)

NC Densidade de estados na banda de condução (cm-3)

ND Concentração de dopantes doadores (cm-3)

ni Concentração intrínseca de portadores (cm-3)

NV Densidade de estados na banda de valência (cm-3)

n(x) Densidade de portadores em um semicondutor (cm-3)

N(x) Densidade de portadores integrada na área da secção transversal de um semicondutor (cm-1)

P Período da estrutura (distância entre o início de um fin e o seu

subseqüente) ( m)

Q Densidade de cargas em um semicondutor (cm-3) q Carga elementar do elétron (q = 1,6 x 10-19 C)

R Resistência de pequenos sinais da estrutura 2-MOS (k) RON Resistência interna ao canal dos dispositivos (k)

RS Resistência série ()

s Área da seção transversal de um semicondutor ( m2)

S Inclinação de sublimiar (mV/década de corrente)

t Tempo (s)

tSi Espessura da camada de silício ( m)

T Temperatura absoluta (K) THD Distorção harmônica total (dB)

THD0 Distorção harmônica total acrescida do nível DC (dB)

Vo Tensão de polarização (V)

Va Amplitude do sinal de entrada senoidal na análise por IFM (V)

VACLM Tensão Early intrínseca devido ao efeito de modulação do comprimento de canal (V)

VB Potencial de substrato (V)

VD Potencial de dreno (V)

VD1 Tensão em uma das entradas de uma estrutura 2-MOS (V)

VDS Tensão aplicada ao dreno do transistor (V)

vds Parcela alternada do sinal aplicada ao dreno do transistor (V)

VEA Tensão Early (V)

VFB Tensão de faixa plana (V)

VG Potencial de porta (V)

VGS Tensão aplicada à porta do transistor (V)

vgs Parcela alternada do sinal aplicada à porta do transistor (V)

VGT = VGS-VTH Sobretensão de porta (V)

Vin Tensão de entrada de um circuito formado por dispositivos MOS (V)

VIN Tensão de entrada das estruturas 2-MOS (V)

Vout Amplitude do sinal de saída senoidal na análise por IFM (V)

VOUT Tensão de saída das estruturas 2-MOS (V)

VS Potencial de fonte (V)

vsat Velocidade de saturação (cm/s)

VTH Tensão de limiar (V)

VX Tensão de entrada de um amplificador operacional (V)

W Largura do canal do dispositivo ( m)

Weff Largura efetiva do canal do dispositivo ( m)

Wfin Largura de fin do FinFET (nm)

Wfin,sim Largura de fin simulada do FinFET ou JL (nm)

LISTA DE ABREVIATURAS

AC Corrente Alternada (Alternating Current)

ALD Atomic Layer Deposition (Deposição de Camada Atômica)

CF Coeficientes de Fourier

CVD Chemical Vapor Deposition (Deposição Química em fase de Vapor)

DC Corrente Contínua (Direct Current)

DIBL Drain Induced Barrier Lowering (Redução da Barreira Induzida pelo Dreno)

DG Double Gate (Transistor de Porta Dupla)

FD Fully Depleted (Completamente Depletado)

FET Field Effect Transistor (Transistor de Efeito de Campo)

FFT Fast Fourier Transformer (Transformada Rápida de Fourier)

GAA Gate-All-Around (Porta Circundante)

GC Graded-Channel (Canal Gradual)

HD Harmonic Distortion (Distorção Harmônica)

IFM Integral Function Method (Método da Função Integral)

IM Inversion Mode ou transistor modo inversão

Imec Interuniversity Microelectronics Center

ITRS International Technology Roadmap for Semiconductors (Mapa da

Tecnologia Internacional para semicondutores) JL Junctionless (Transistor sem junção)

MOS Metal-Oxide-Semiconductor (Metal-Óxido-Semicondutor)

OTA Operational Transconductance Amplifier (Amplificador Operacional de

Transcondutância)

PD Partially Depleted (Parcialmente Depletado)

SCE Short Channel Effects (Efeitos de Canal Curto)

sCESL strained Contact Etch Stop Layer

SOI Silicon-on-Insulator (Silício sobre Isolante)

sSOI Strained Silicon-on-Insulator (Silício sobre Isolante Tensionado)

UCC University College Cork

UCL Université Catholiquede Louvain

VIP Voltage Interception Point (Tensão de Intersecção)

SUMÁRIO

1 INTRODUÇÃO ... 27

1.1 OBJETIVOS E ESTRUTURA DO TRABALHO ... 32

2 CONCEITOS FUNDAMENTAIS ... 35

2.1 TRANSISTORES SOI DE MÚLTIPLAS PORTAS ... 35

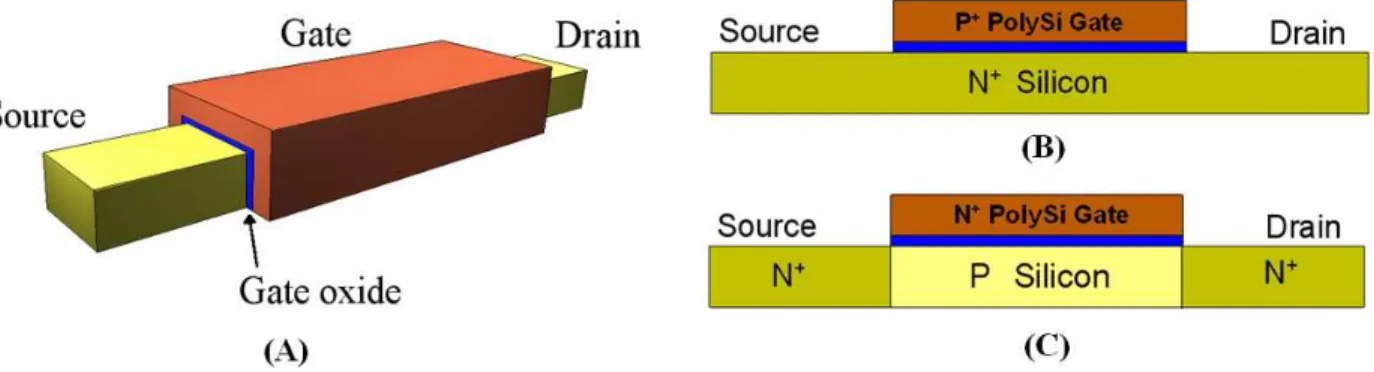

2.1.1 Dispositivos FinFET ... 36 2.1.2 Dispositivo SOI Gate-All-Around (GAA) ... 42 2.1.3 Transistor Sem Junções (Junctionless – JL) ... 45

2.2 CARACTERÍSTICAS ANALÓGICAS ... 47

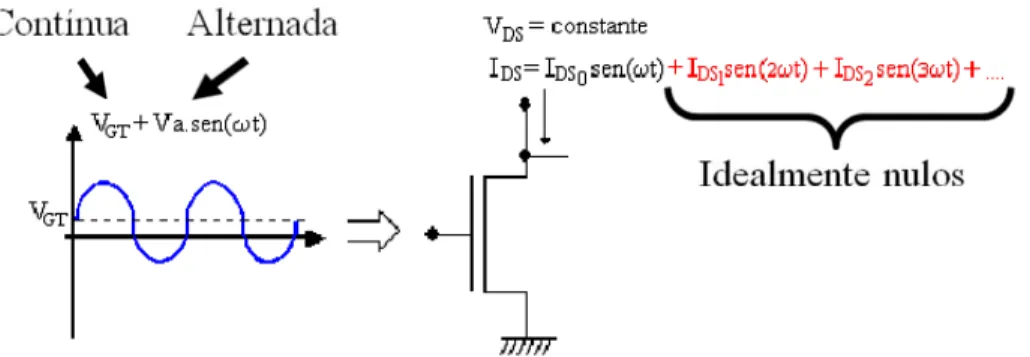

2.2.1 Não-Linearidade ou Distorção Harmônica ... 48

2.2.1.1 Método de Fourier ... 50 2.2.1.2 Método da Série de Taylor ... 52 2.2.1.3 Método da Função Integral (IFM) ... 55

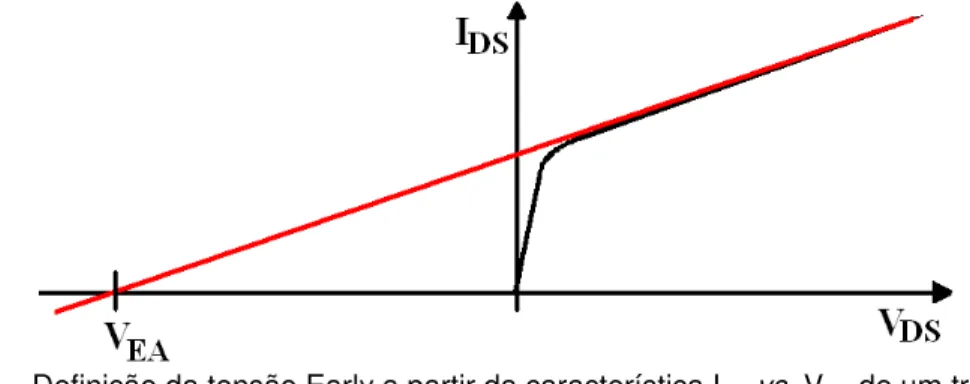

2.2.2 Características Analógicas de Dispositivos Operando como Amplificadores ... 61

2.2.2.1 Tensão Early e Condutância de Dreno ... 62 2.2.2.2 Ganho de Tensão em Malha Aberta ... 64 2.2.2.3 Razão gm/IDS ... 64

2.2.2.4 Freqüência de Ganho Unitário ... 66

2.2.3 Características Analógicas de Dispositivos Operando como Resistores 66

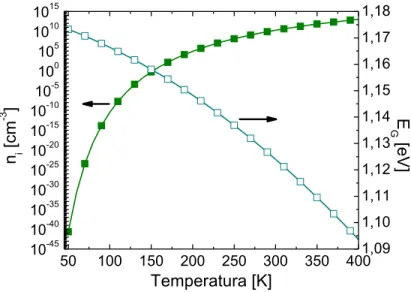

2.2.3.1 Estrutura 2-MOS ... 67 2.3 APLICAÇÃO DE TENSÃO MECÂNICA ... 70 2.4 EFEITOS DE REDUÇÃO DA TEMPERATURA ... 73

2.4.1 Parâmetros Físicos dos Semicondutores Dependentes da Temperatura 73 2.4.2 Parâmetros Elétricos do Transistor SOI Dependentes da Temperatura... 76

2.5 SIMULADORES UTILIZADOS ... 79

3.1 LINEARIDADE EM FINFETS DE PORTA TRIPLA CONVENCIONAIS E DE CANAL TENSIONADO OPERANDO EM SATURAÇÃO ... 85

3.1.1 Características dos Dispositivos e Medidas Experimentais ... 85 3.1.2 Distorção Harmônica Desprezando o Ganho de Tensão em Malha Aberta ... 90 3.1.3 Origens Físicas das Não-Linearidades ... 97 3.1.4 Distorção Harmônica Considerando o Ganho de Tensão em Malha Aberta ... 102 3.1.5 Distorção Harmônica em Função da Temperatura ... 107

3.2 LINEARIDADE EM ESTRUTURAS 2-MOS COMPOSTAS POR

DISPOSITIVOS FINFETS CONVENCIONAIS E TENSIONADOS ... 114

3.2.1 Características do Circuito e dos Dispositivos ... 115 3.2.2 Avaliação da Distorção Harmônica em Estruturas Compostas por

FinFETs Convencionais ... 116 3.2.3 Avaliação da Distorção Harmônica em Estruturas Compostas por

FinFETs com a Presença de Tensão Mecânica ... 124 3.2.4 Avaliação de HD3 em Termos da Resistência on (RON) ... 127

3.3 LINEARIDADE EM ESTRUTURAS 2-MOS COMPOSTAS POR

DISPOSITIVOS GC GAA EM FUNÇÃO DA TEMPERATURA ... 131

3.3.1 Características dos Dispositivos e Medidas Experimentais ... 131 3.3.2 Análise da Distorção Harmônica ... 134 3.3.3 Origens Físicas das Não-Linearidades ... 137 3.3.4 Avaliação de HD3 em Temperaturas Criogênicas ... 140

3.4 COMPORTAMENTO ANALÓGICO E LINEARIDADE EM TRANSISTORES SEM JUNÇÕES OPERANDO EM SATURAÇÃO ... 144

3.4.1 Características dos Dispositivos ... 145 3.4.2 Parâmetros Analógicos... 147 3.4.3 Discussão Física sobre o Funcionamento do Transistor sem Junções . 150 3.4.4 Efeito da Temperatura nos Parâmetros Analógicos ... 157 3.4.5 Distorção Harmônica ... 164

REFERÊNCIAS BIBLIOGRÁFICAS ... 172

APÊNDICE A – SIMULAÇÃO ATLAS FINFET ... 187

APÊNDICE B – SIMULAÇÃO ATHENA GC GAA ... 192

APÊNDICE C – SIMULAÇÃO DE CIRCUITOS GC GAA ... 195

1 INTRODUÇÃO

A redução das dimensões dos dispositivos, decorrente da evolução da microeletrônica, tem imposto diversos desafios tecnológicos à aplicação de transistores de efeito de campo planares da tecnologia Metal-Óxido-Semicondutor ( Metal-Oxide-Semiconductor Field-Effect-Transistor – MOSFET). Com a miniaturização dos

dispositivos, o controle das cargas na região do canal pela porta se torna menos efetivo, devido à maior proximidade entre as regiões de fonte e dreno do transistor e a conseqüente interação de suas regiões de depleção com aquela originária da porta, proporcionando a ocorrência de efeitos de canal curto. Devido às dificuldades encontradas na aplicação de transistores MOS convencionais, diversos dispositivos com características elétricas superiores, tais como, maior corrente e inclinação de sublimiar mais próxima do ideal, têm sido desenvolvidos em tecnologias mais avançadas, com o intuito de aumentar a sobrevida de transistores de efeito de campo.

Entre os dispositivos mais promissores 1, estão aqueles fabricados na

tecnologia Silício sobre Isolante (Silicon-on-Insulator – SOI), em que uma camada de

material isolante, normalmente chamada de óxido enterrado, separa a região ativa da lâmina (onde são fabricados os dispositivos) do substrato. Este isolamento é responsável por uma série de melhorias nas características elétricas de dispositivos com comprimento reduzido de canal, como a redução das capacitâncias de junção de fonte e dreno 1 e a redução da dependência da tensão de limiar dos dispositivos com o comprimento de canal. Esta redução se deve ao maior controle das cargas de depleção

1. Outra vantagem observada em transistores desenvolvidos em lâminas SOI diz

respeito à grande diminuição do efeito de corpo em relação a dispositivos MOS fabricados em tecnologia convencional, embora esta vantagem seja observada apenas em dispositivos que possuam a camada de silício na região ativa suficientemente fina, de modo que toda a camada de silício esteja em depleção (transistor completamente depletado) 2.

com camada de silício na região ativa mais espessa (parcialmente depletados) como a redução na corrente de fuga 1 e a degradação por portadores quentes, devido à

ionização por impacto. Além disso, a tecnologia SOI apresenta, sobretudo para dispositivos completamente depletados, grande potencial de aplicação em sistemas de baixo consumo de potência 3.

Embora dispositivos planares fabricados em tecnologia SOI apresentem características superiores aos MOSFETs convencionais, como melhor inclinação de sublimiar e menor efeito de corpo, diversos outros tipos de transistores, também desenvolvidos a partir da tecnologia SOI, têm apresentado características elétricas ainda melhores. Entre os mais promissores estão aqueles chamados de transistores de múltiplas portas. Tais dispositivos possuem mais de uma porta associada à sua região de canal, proporcionando um maior controle das cargas espaciais e reduzindo efeitos decorrentes da redução das dimensões 4. Além disso, com a aplicação de potencial à porta, toda a camada de silício pode se depletar, aumentando a transcondutância (gm) e

resultando em um maior ganho de tensão em malha aberta (AV) quando comparado ao

transistor SOI planar 5. Neste trabalho serão estudados alguns dos transistores de

múltiplas portas mais promissores, como o dispositivo de porta circundante ( Gate-All-Around – GAA) 6, o FinFET 7 e o transistor sem junções (Junctionless– JL) 8.

Embora possuam a região de canal envolta por óxido e material de porta, os transistores GAA são considerados dispositivos de porta dupla, uma vez que a espessura da camada de silício é bastante inferior à sua largura e os canais formados em suas laterais podem ser desprezados. Os transistores GAA estudados ao longo deste trabalho possuem uma configuração peculiar, que consiste em um perfil assimétrico de dopantes na região de canal (Graded-Channel – GC) 9,10, onde a

concentração de dopantes natural da lâmina é mantida na região próxima ao dreno, enquanto que no restante do canal é feita uma implantação iônica para o ajuste da tensão de limiar (VTH). Esta configuração visa a reduzir os efeitos decorrentes do forte

a estrutura GC promove um grande aumento do ganho de tensão em malha aberta, redução da condutância de saída e aumento da transcondutância, que são fundamentais em aplicações analógicas. Ao unir as estruturas GAA e GC, as vantagens proporcionadas por cada uma delas se somam, tornando o dispositivo final (GC GAA) ainda mais interessante para aplicações analógicas 5,16,17. De acordo com a referência [5], o ganho de tensão de malha aberta apresentado pelo GC GAA resultou em uma melhora significativa de 30~40 dB em relação a um dispositivo GC de porta simples e de 20~30 dB em um GAA uniformemente dopado de dimensões similares. A aplicação da estrutura GC em um transistor planar de porta simples mostrou melhorar o seu ganho de tensão de 38 dB para 52 dB 13.

FinFETs, por sua vez, são dispositivos que possuem canal vertical e podem ser transistores de porta dupla ou tripla, dependendo de seu processo de fabricação 7. Os dispositivos FinFETs estudados ao longo do trabalho possuem toda a região de canal com baixo nível de concentração de dopantes, ou seja, a concentração de dopantes natural da lâmina é intencionalmente mantida, não havendo implantação iônica para ajuste da tensão de limiar, que é controlada diretamente pela função trabalho do material de porta 18. Assim, a estes transistores não é aplicada a estrutura GC. Diversos

trabalhos têm mostrado as vantagens proporcionadas por FinFETs sobre dispositivos de porta simples decorrentes do melhor controle das cargas de canal 19.

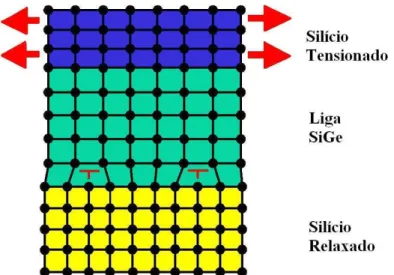

Parte dos FinFETs analisados é fabricada sobre lâminas SOI tensionadas (sSOI). Estas lâminas podem ser obtidas através do crescimento epitaxial de uma liga relaxada de SixGe1-x, com a deposição de silício monocristalino tensionado em sua

superfície 20. A tensão mecânica tem sido bastante utilizada em tecnologias recentes, com o intuito de aumentar a mobilidade em dispositivos MOS 21 e pode ser uniaxial (apenas na direção do canal do dispositivo) ou biaxial (nas direções do canal e da largura do dispositivo), dependendo de seu processo de fabricação. A tensão uniaxial pode ser obtida através da deposição de uma camada de Si3N4 sobre o dispositivo

(strained Contact Etch Stop Layers – sCESL) 22, enquanto que a biaxial deriva de

fuga em relação a FinFETs convencionais 23,24. Apesar disso, poucos estudos tratam

das propriedades analógicas de FinFETs convencionais ou tensionados.

Os transistores sem junção constituem nanofios de silício de porta tripla, similares às estruturas dos FinFETs. No entanto, diferentemente destes, não possuem junções fonte/canal e canal/dreno. Diferentemente dos FinFETs, onde os dopantes de fonte e dreno (p ou n) são de tipo contrário ao do canal, o JL apresenta um perfil constante de dopantes entre fonte, canal e dreno (tipo n nos dispositivos nMOS e tipo p nos pMOS). Estes dispositivos foram recentemente desenvolvidos com o intuito de reduzir a complexidade no processo de fabricação de dispositivos nanométricos 8. Idealmente, quanto mais abruptas forem as junções de um transistor, ou seja, quanto menor for a região de transição da concentração de dopantes do canal para a fonte ou o dreno, melhor será o comportamento elétrico dos dispositivos estudados 25. Devido à miniaturização dos dispositivos, as junções devem apresentar uma transição ainda mais abrupta uma vez que a concentração de dopantes tem que variar em diversas ordens de magnitude em alguns nanômetros. Assim, se torna necessário um controle extremamente preciso das condições térmicas e de concentração de dopantes para evitar a difusão de impurezas na região do canal 25. Devido ao peculiar perfil de

dopantes, os dispositivos JL operam em regime de acumulação, diferentemente dos demais transistores estudados, os quais funcionam em modo inversão 25.

Embora seja de fundamental importância em diversos circuitos analógicos tais como filtros, conversores analógico-digitais e sistemas de áudio, a não-linearidade em transistores de múltiplas portas tem sido pouco estudada. A não-linearidade dos dispositivos, comumente denominada de distorção harmônica, está presente em qualquer dispositivo MOS 26. Ao se aplicar um sinal alternado (normalmente senoidal) na entrada de um sistema não-linear, este sistema gerará em sua saída um sinal na mesma freqüência do sinal de entrada, chamado de sinal fundamental, e diversos outros sinais de freqüências diferentes 26. Quanto mais desprezíveis forem estes sinais frente ao fundamental, menor será a distorção associada ao sistema. Neste trabalho será feito um estudo sobre o comportamento analógico dos dispositivos FinFETs e GC GAAs com vistas à AV, gm, gD e resistência de canal, dando ênfase ao estudo das

envolvendo transistores sem junção será focado, principalmente, em seus parâmetros analógicos, embora suas figuras de mérito de não-linearidade também sejam apresentadas. O estudo envolvendo os diferentes dispositivos utilizados será estendido para aplicações em função temperatura (T).

Inicialmente, será feita a análise das não-linearidades apresentadas experimentalmente por FinFETs, operando como amplificadores na região de saturação, em função do comprimento do dispositivo (L) e da largura do fin (Wfin). Neste

estudo serão determinadas as distorções harmônicas de segunda e de terceira ordens (HD2 e HD3, respectivamente) na saída dos dispositivos. HD2 representa a maior fonte de não-linearidade em amplificadores unitários, sendo o principal responsável pela distorção harmônica total (THD), enquanto que HD3 constitui o harmônico de terceira ordem, que é de extrema importância em circuitos diferenciais 27. Neste estudo, procurar-se-á determinar também as origens físicas das não-linearidades apresentadas por FinFETs, através da aplicação de modelos analíticos e simulações. Além disso, será observada a influência de AV na não-linearidade dos dispositivos.

Na seqüência, a distorção harmônica destes mesmos transistores será avaliada quando estiverem operando na região triodo, como resistores quase-lineares 28,29. Com

o intuito de reduzir a distorção ao longo desta análise, os dispositivos serão aplicados a circuitos balanceados compostos por dois transistores (2-MOS) 27, uma vez que tais

circuitos suprimem a distorção gerada por harmônicos pares, que normalmente é dominante, e a não-linearidade passa e ser dada, fundamentalmente, por HD3. Como se tratam de circuitos resistivos, neste estudo, HD3 será avaliado também em função da resistência apresentada pelos dispositivos (RON), que normalmente é requisito do

projeto. Neste caso, também serão determinadas as fontes das não-linearidades.

Na seqüência, será avaliada, através de HD3, a distorção apresentada por dispositivos GC GAA operando em triodo, aplicados a estruturas 2-MOS, em função do comprimento da região de canal fracamente dopada (LLD). Este estudo, baseado em

medidas experimentais de dispositivos e simulações de estruturas 2-MOS, complementa a avaliação de GC GAAs, operando em saturação, apresentada na ref. [17] e procurará explicar a origem das não-linearidades apresentadas pelos transistores. Este estudo, inicialmente feito em temperatura ambiente, foi estendido para temperaturas criogênicas de até 100 K.

Finalmente, serão apresentadas as principais características analógicas de transistores JL, tais como a razão da transcondutância pela corrente de dreno (gm/IDS),

a tensão Early (VEA) e o ganho de tensão em malha aberta (AV), comparando os

parâmetros analógicos apresentados por estes dispositivos aos exibidos por transistores de porta tripla ou FinFETs modo inversão (IM). O estudo será efetuado para dispositivos operando em saturação como amplificadores unitários e considerará a dependência das propriedades analógicas com Wfin e com a temperatura. Além disso,

este trabalho procurará identificar as razões físicas dos resultados obtidos através de simulações tridimensionais. A partir deste estudo serão extraídas as não-linearidades (através de HD2 e HD3) dos dispositivos.

Para a obtenção das características de não-linearidade (HD2 e HD3) dos transistores, será utilizado o método da função integral (Integral Function Method – IFM) 30, que é um método matemático que permite a obtenção da linearidade a partir das

curvas obtidas em corrente contínua.

1.1 OBJETIVOS E ESTRUTURA DO TRABALHO

operando em triodo. Embora seja de grande importância em diversos circuitos analógicos, a resposta de tais dispositivos em termos de distorção permanece desconhecida. Tanto em FinFETs como em GC GAAs, o estudo em triodo é feito através da aplicação de estruturas balanceadas, que proporcionam aumento na linearidade. Além disso, as propriedades analógicas e a distorção harmônica de dispositivos JL serão avaliadas quando estes estiverem operando em regime de saturação. Diversas das análises efetuadas considerarão a influência da temperatura nos resultados obtidos. FinFETs com e sem tensão mecânica, GC GAAs e transistores sem junção foram escolhidos para o estudo atual devido ao interesse que tais dispositivos de múltiplas portas têm despertado na comunidade científica como pode ser observado em [19],[21],[25].

Este trabalho foi dividido em quatro capítulos, dispostos conforme pode ser observado a seguir.

O Capítulo 2 trata dos conceitos teóricos necessários para o entendimento do trabalho. Neste capítulo, serão abordados os fundamentos básicos dos transistores FinFET, GC GAA e JL, e em seguida, será feita uma introdução às características analógicas dos dispositivos. Na seqüência, será efetuada uma explanação sobre os conceitos de não-linearidade e distorção harmônica, culminando com os métodos de sua extração, em especial do IFM, e serão introduzidas as estruturas balanceadas 2-MOS. Adiante, será abordada a aplicação de tensão mecânica nos dispositivos e, finalmente, serão apresentados alguns tópicos sobre a redução da temperatura.

as propriedades analógicas dos JL serão comparadas às de dispositivos FinFETs de porta tripla, também denominados Trigate.

2 CONCEITOS FUNDAMENTAIS

Este capítulo apresenta uma introdução teórica, onde são abordados os principais conceitos necessários para a compreensão do trabalho. Inicialmente, será apresentado o FinFET 7, serão abordadas as características básicas dos transistores de porta circundante Gate-All-Around 6 com estrutura de canal gradual 10 e então serão

introduzidos os transistores sem junção (Junctionless – JL) e suas principais

características. Na seqüência, um tópico tratará dos principais conceitos envolvendo não-linearidades, culminando com os principais métodos de sua extração e, então, será feita uma introdução às características analógicas dos dispositivos e serão apresentadas as estruturas balanceadas compostas de 2 transistores (2-MOS). Adiante, serão introduzidos os principais conceitos relacionados à aplicação de tensão mecânica aos dispositivos e, finalmente, abordados alguns tópicos sobre a operação dos dispositivos em baixas temperaturas.

2.1 TRANSISTORES SOI DE MÚLTIPLAS PORTAS

Com a evolução da microeletrônica e a conseqüente miniaturização dos dispositivos, diversos problemas decorrentes da redução das dimensões dos transistores vieram à tona, como os efeitos de canal curto. Assim, diversos dispositivos de múltiplas portas vêm sendo desenvolvidos, buscando a redução ou mesmo supressão destes problemas, visando à obtenção de melhores características elétricas, como maior intensidade de corrente, inclinação de sublimiar mais próxima do valor ideal de 60 mV/década 19, redução do efeito de corpo, entre outras 1. Entre os principais dispositivos de porta dupla (Double Gate – DG) desenvolvidos, pode-se mencionar:

XMOS 31, MFXMOS 32,33, Gate-All-Around 6, DELTA (Fully Depleted Lean-Channel Transistor) 34, condutor triangular (triangular-wired) 35,36 e FinFET 7. Dentre aqueles de

dispositivos com portas tripla+ como o -gate 39 e o -gate 40 e com porta circundante como o CYNTHIA 41 e o TSNWFET 42. Embora desenvolvido recentemente, o transistor sem junções 8 dispõe de uma estrutura semelhante ao Trigate ou FinFET de porta tripla e tem sido alvo de diversos estudos que o credenciam a compor esta lista.

Neste tópico será dada uma breve explicação sobre as estruturas SOI completamente depletadas aplicadas a dispositivos de múltiplas portas. Na introdução teórica apresentada, será dada ênfase aos dispositivos GAA, FinFET e JL, os quais se apresentam como alguns dos mais promissores para o futuro da microeletrônica. Nesta seção também serão abordadas as principais características elétricas dos dispositivos.

2.1.1 Dispositivos FinFET

Os transistores FinFET podem ser considerados como uma evolução do dispositivo DELTA 34, o primeiro dispositivo de porta dupla já fabricado. Assim como ocorre com o DELTA, o dispositivo FinFET apresenta canais de condução verticais diferentemente do transistor planar. Deste modo, o FinFET é fabricado sobre uma ilha de silício alta e estreita, que é chamada de finger, leg ou simplesmente fin. A estrutura

FinFET é bastante similar à DELTA e só difere desta última devido à presença de uma camada dielétrica, chamada hard mask, no topo da camada de silício. Este dielétrico

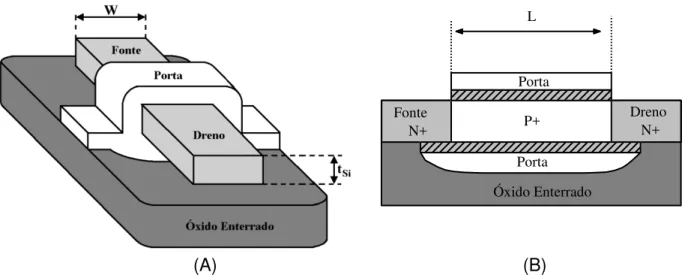

evita a inversão dos cantos superiores do dispositivo, prevenindo a formação de canais parasitas. Na Figura 2.1, podem-se observar as estruturas esquemáticas do dispositivo DELTA e do FinFET.

Embora o dispositivo DELTA apresente portas nas laterais e no topo da camada de silício, este transistor pode ser considerado como um dispositivo de porta dupla já que a altura do fin é bem superior à sua largura 43. No entanto, atualmente, existem

alguns dispositivos chamados Trigate em que a largura e a altura do fin são mais

(A) (B)

Figura 2.1 – Estruturas de transistores de porta dupla: (A) FinFET e (B) MOSFET DELTA.

FinFETs de porta dupla ou tripla possuem diversas características que os tornam mais atrativos que dispositivos de porta simples com dimensões similares. A tecnologia de múltiplas portas apresenta melhores resultados em termos de transcondutância (gm),

efeitos de canal curto, inclinação de sublimiar (S) e intensidade de corrente (IDS), entre

outros 1. Estas características, além de outras, serão detalhadas a seguir.

Uma importante vantagem apresentada por dispositivos de múltiplas portas, diz respeito à maior transcondutância quando comparado a dispositivos de porta simples. A transcondutância é definida como a derivada da corrente IDS em função da tensão de

porta (VGS) e representa a eficácia do controle da tensão de porta sobre a corrente.

Nestes dispositivos, gm resulta em um valor que pode superar o dobro do valor obtido

em transistores SOI de porta simples 6.

Embora o valor teórico máximo da transcondutância em um dispositivo de porta dupla seja o dobro daquele observado em transistores de porta simples, tais dispositivos podem exibir uma transcondutância ainda maior. Isto se deve ao fenômeno da inversão de volume, presente em dispositivos totalmente depletados (Fully-Depleted

que nas interfaces 44, a mobilidade efetiva (eff) nas proximidades das interfaces se

torna inferior à apresentada no interior da camada de silício. Este aumento na mobilidade se reflete em um incremento da transcondutância, uma vez que existe uma relação direta entre mobilidade e transcondutância (gm eff).

Por se tratar de um fenômeno quântico, a concentração de elétrons não pode ser calculada unicamente com a solução da equação de Poisson em dispositivos com a presença de inversão de volume, pois esta leva em conta apenas a física clássica. À equação de Poisson, deve-se adicionar a solução da equação de Schrödinger 45, que trata de fenômenos quânticos. Normalmente, a inversão de volume se torna importante em dispositivos de camada de silício com espessura inferior a 30 nm 6. Um esquema da inversão de volume presente em dispositivos de camada fina é mostrado na Figura 2.2.

Poisson

Poisson + Schrödinger

Profundidade no Silício

Profundidade no Silício

C

on

ce

nt

ra

çã

o d

e E

lé

tr

on

s

0 tSi 0 tSi

(A) (B)

Figura 2.2 – Esquema da inversão de volume em um MOSFET de porta dupla com filme fino em (A) VGS ≤ VTH e em (B) VGS > VTH 6.

Embora a corrente de dreno tenha relação direta com a mobilidade, IDS é dada,

principalmente, pela razão W/L efetiva e pela tensão de limiar do dispositivo de múltiplas portas. Deste modo, a corrente de dreno é essencialmente igual à soma das correntes fluindo através de todas as interfaces cobertas por óxido de porta. Assim, a corrente através do FinFET porta dupla torna-se próxima ao dobro da corrente do dispositivo convencional de porta simples e a corrente do Trigate é próxima ao triplo da corrente do dispositivo convencional (considerando as três portas com comprimentos de canal semelhantes) 46. Entretanto, a corrente final costuma ser menor que o valor

alteração conforme a orientação cristalográfica do silício. A mobilidade dos elétrons nas superfícies laterais costuma ser inferior à da superfície superior, já que as laterais costumam ter orientação (110), enquanto que o topo da lâmina tem orientação (100) 47.

Com o objetivo de aumentar a corrente, são utilizados multi-dedos, ou seja, diversos fins são conectados em paralelo, de forma que a corrente total seja dada pela

corrente de cada fin multiplicado pelo número de fins (considerando que a mobilidade

seja igual em todas as interfaces óxido-silício). Uma estrutura multi-dedos ou multi-fins

é representada na Figura 2.3. A corrente apresentada pelo transistor multi-fins (IDmulti) é

relacionada com aquela que flui em um transistor planar por unidade de largura de canal (ID0) através da equação (2.1).

Figura 2.3 – Estrutura multi-dedos ou multi-fins.

P H 2 W I

I fin fin

0 D Dmulti

(2.1)

onde Hfin é a altura de um fin e P é o período da estrutura, ou seja, a distância entre o

início de um fin e o seu subseqüente. Para que a estrutura multi-fin seja vantajosa, a

corrente IDmulti deverá ser maior que ID0. Em dispositivos de porta tripla, onde a largura e

a altura do fin são iguais, P deve ser menor que 3Wfin para que a corrente no multi-fin

seja maior que em um dispositivo de porta simples de dimensões equivalentes 48. Assim como em outros dispositivos de múltiplas portas, nos FinFETs a tensão de limiar se dá em valores inferiores ao dobro do potencial de Fermi (F) devido ao

mecanismo de inversão fraca 49. Para dispositivos extremamente estreitos, no entanto, a condução poderá ocorrer em valores superiores a 2F 19. Dispositivos de porta tripla

prematura da região onde existe a união das portas laterais com a porta superior, dando origem a correntes parasitas indesejáveis, devido à maior influência do campo nestas regiões. O efeito de canto pode ser atenuado ou mesmo suprimido ao se utilizar cantos com grandes raios de curvatura ou uma dopagem reduzida no canal. Neste caso, a tensão de limiar pode ser controlada com o uso de um midgapmaterial (material

com função trabalho próxima à do silício intrínseco – em torno de 4,7 eV) como material de porta 50.

Outro parâmetro de suma importância no estudo de transistores, especialmente de dimensões submicrométricas, consiste nos efeitos de canal curto (Short Channel Effects – SCE), que são responsáveis por uma dependência indesejável da tensão de

limiar com o comprimento de canal dos dispositivos 46. Além disso, esses efeitos provocam um aumento da corrente de fuga e uma degradação na inclinação de sublimiar dos dispositivos 46.

Os efeitos de canal curto são provocados pela redução do controle das cargas no interior do canal pela porta. Em transistores de canal curto, o campo elétrico resultante das regiões de depleção de dreno e fonte passam a exercer maior influência nas cargas da região de canal, passando a competir com a porta pelo seu controle. Este efeito é menos pronunciado em transistores de múltiplas portas em comparação aos dispositivos de porta simples, uma vez que ao se aumentar a quantidade de portas de um dispositivo, o controle de cargas na região do canal aumenta 19. A fim de

determinar a influência dos efeitos de canal curto em um FinFET de porta dupla pode-se calcular o comprimento natural da estrutura () que representa a distância de penetração das linhas de campo elétrico do dreno no interior do corpo do dispositivo, expressa através da equação (2.2) 19.

Si OX OX Si t t 2

(2.2)

onde Si e OX são as permissividades do silício e do óxido, tOX a espessura da camada

de óxido e tSi a espessura da camada de silício que, em FinFETs de porta dupla,

planar é dado por OX Si

OX Si t t

. Logo, pode-se notar que o valor de é 1/ 2 menor em dispositivos de porta dupla em relação aos planares. Quanto menor for o comprimento natural, maior a imunidade do dispositivo à efeitos de canal curto.

Nos FinFETs de porta tripla, o comprimento natural passa a ter um valor intermediário entre o obtido pela equação (2.2), para dispositivos de porta dupla, e aquele dado pela equação (2.3), para dispositivos de quatro portas.

Si OX OX Si t t 4

(2.3)

Através das equações referentes ao comprimento natural, pode-se determinar as espessuras mínimas das camadas de óxido e de silício para que o dispositivo fique livre dos efeitos de canal curto. Para que isso ocorra, o comprimento de canal do transistor deve ser de 5 a 10 vezes maior que o comprimento natural do dispositivo 51.

Devido à presença de duas ou três portas, a inclinação de sublimiar obtida no dispositivo FinFET, expressa através da equação (2.4), apresenta uma significativa melhora em relação aos transistores convencionais, com valores próximos ao limite teórico de 60 mV/década em temperatura ambiente 19.

) I log(

V S

DS GS

(2.4)

Assim como no caso dos efeitos de canal curto, a melhor inclinação de sublimiar se deve ao maior controle das cargas no interior do canal. No entanto, a inclinação de sublimiar pode adquirir valores superiores se o efeito de redução da barreira junto à fonte induzida pelo dreno (Drain Induced Barrier Lowering – DIBL) estiver presente. O

transistores de múltiplas portas este efeito é sensivelmente menor que em transistores SOI planares 19.

Embora o fenômeno da ionização por impacto altere as características de sublimiar, este fenômeno é sensivelmente menor nos dispositivos de múltiplas portas em relação ao apresentado por dispositivos de porta simples parcialmente ou completamente depletados (Partially e Fully Depleted– PD e FD, respectivamente) 52.

2.1.2 Dispositivo SOI Gate-All-Around (GAA)

O transistor SOI de porta circundante (GAA), exibido na Figura 2.4, foi desenvolvido em 1990 6 e pode ser considerado como um dispositivo de porta dupla, embora todo o seu canal seja envolvido por isolante e material de porta, pois como a largura do seu canal é muito maior que a espessura do filme de silício, o efeito das portas nas laterais do canal podem ser desprezados. Como o canal fica na posição horizontal, diferentemente da maior parte dos transistores apresentados até agora, que exibem canal vertical, este dispositivo pode ser fabricado a partir do processo de um transistor SOI de porta simples, com a necessidade de apenas algumas modificações, apresentadas na referência 6.

Porta Porta

Fonte N+

Dreno N+

Óxido Enterrado P+

L

(A) (B)

Muitas das vantagens apresentadas para os FinFETs de porta dupla e tripla continuam válidas para os dispositivos GAAs, como a maior transcondutância resultante do fenômeno de inversão de volume 6. Neste caso, o fenômeno da inversão é semelhante ao relatado para dispositivos FinFETs. De fato, a inversão de volume foi constatada primeiramente em transistores GAAs e, algum tempo depois, nos demais dispositivos 19. Outra vantagem mantida em dispositivos GAAs é o aumento da corrente de dreno, que é essencialmente igual à soma das correntes fluindo através de todas as interfaces cobertas por óxido de porta. Assim, a corrente através do GAA torna-se próxima ao dobro da corrente do dispositivo convencional de porta simples 19.

Da mesma forma como ocorrem em FinFETs, em dispositivos GAAs, a determinação da tensão de limiar se torna impossível a partir da definição convencional em que a inversão forte se dá quando o potencial de superfície (S) atinge duas vezes

ao potencial de Fermi. Nos transistores GAAs, a tensão de limiar pode ser obtida com tensão de porta de 10 mV a 90 mV inferiores àquela que levaria ao dobro do potencial de Fermi 6. Assim, para estes dispositivos, a tensão de limiar deve ser determinada por métodos alternativos 49 como, por exemplo, o ponto de máximo da segunda derivada da corrente de dreno em função de tensão de porta.

Devido à presença de múltiplas portas possibilitando o melhor controle das cargas na região de canal, os efeitos de canal curto e a inclinação de sublimiar apresentadas pelo GAA são semelhantes aos descritos para os FinFETs no item anterior. Como GAAs são considerados dispositivos de porta dupla, o comprimento natural é dado pela equação (2.2), da mesma forma como ocorrem com FinFETs de porta dupla.

Uma importante desvantagem dos dispositivos SOI em relação ao MOS convencional consiste no efeito de auto-aquecimento (self-heating). A camada de óxido

simples uma vez que não possuem óxido enterrado diretamente abaixo do canal, mas uma camada de silício policristalino e uma fina camada de óxido de porta 53.

Devido ao processo de fabricação utilizado, o dispositivo resultante tem uma porta inferior mais longa que a superior, como observado na Figura 2.4 (B), o que representa uma maior capacitância parasita, como apresentado em 54. No entanto, recentemente, GAAs com comprimento de canal de 50 nm foram fabricados com sucesso, na qual o problema das portas desalinhadas foi suprimido, demonstrando o interesse despertado por esta estrutura 55.

Como mencionado anteriormente, o processo de fabricação utilizado permite que o transistor GAA seja construído com uma arquitetura assimétrica de canal, conhecida por canal gradual (Graded-Channel– GC), que propicia diversas vantagens em circuitos

voltados para aplicações analógicas 10. Inicialmente apresentada em 2000, a arquitetura GC apresenta dois perfis distintos de dopagem no interior do canal, conforme pode ser observado na Figura 2.5, que apresenta o corte transversal de um dispositivo GAA com arquitetura GC.

Porta Porta

Fonte N+

Dreno N+

Óxido Enterrado

P+

P-LLD L

Figura 2.5 – Corte transversal do dispositivo de porta circundante com arquitetura de canal gradual (GC GAA).

Em uma região de comprimento LLD, próxima ao dreno, não ocorre a implantação

iônica para ajuste da tensão de limiar e a concentração de dopantes é mantida igual à concentração natural da lâmina. Deste modo, a implantação é feita apenas na região próxima à fonte, que se torna responsável pelo controle da tensão de limiar. Assim, o comprimento efetivo de canal do dispositivo passa a ser dado por Leff = L - LLD. Nestes