CAPÍTULO 12 – CONVERSORES DIGITAL/ANALÓGICO (D/A) E

ANALÓGICO/DIGITAL (A/D)

(Sistemas Digitais: Princípios e Aplicações / TOCCI, R. J.; WIDMER, N. S. / Capítulo 10)

1. Introdução

A maioria das grandezas físicas é analógica e estas possuem valores contínuos. Exemplos: tensão, corrente, som, temperatura, pressão, velocidade etc.. A figura 1.1 ilustra a variação da velocidade de um automóvel:

! "#$% &

'" & ()

*) +) ,) -() -))

- ( . * / + 0 , 1 -)

Figura 1.1 – Gráfico da velocidade.

Note que para a velocidade passar de 40km/h para 60km/h a velocidade passa por uma infinidade de valores intermediários. As variáveis físicas analógicas podem assumir qualquer valor dentro de uma faixa de valores contínuos.

Num processo de digitalização de uma grandeza analógica efetuam-se amostragens a cada intervalo de tempo para a conversão. Na figura 1.2 temos a ilustração do gráfico da velocidade com amostragem sendo efetuada a cada segundo. No caso do velocímetro digital a amostragem em intervalos de um segundo é suficiente para que o motorista possa efetuar a leitura no mostrador digital (display). Para cada situação é necessário efetuar a análise do intervalo de tempo necessário para a amostragem. Quanto mais bits forem utilizados maior será a precisão da informação digital, porém o circuito torna-se mais complexo.

! "#$% &

+) ,) -() -))

-)

)

-)

-)

-)

-)

)

-)

)

)

)

-)

-)

Para os circuitos digitais manipularem ou armazenarem as informações analógicas é necessário a conversão para a forma digital. As informações na forma digital possuem algumas vantagens, entre as quais podemos citar:

a) A maior facilidade de armazenamento de dados; b) Possibilidade de compactar as informações;

c) Armazenamento e transmissão de maior quantidade de informações; d) Maior imunidade a ruídos.

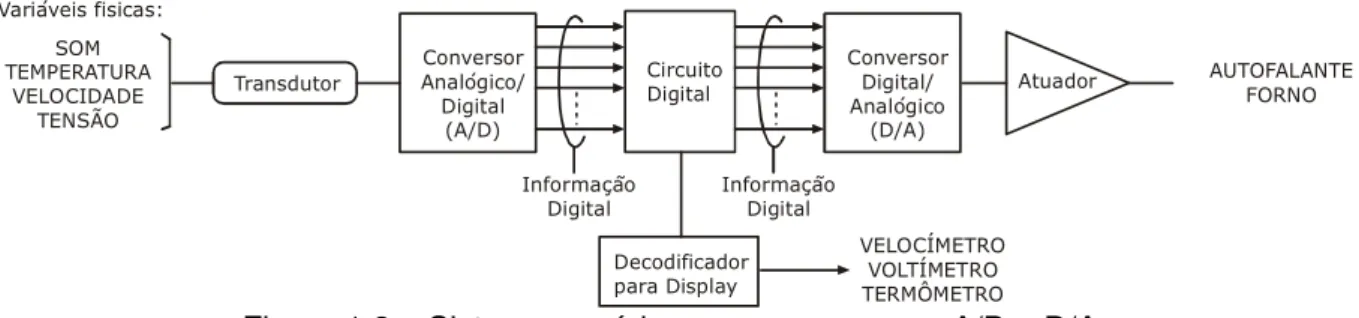

Na figura 1.3 temos a ilustração de um sistema genérico com conversores Analógico/Digital (A/D) e Digital/Analógico (D/A). Dependendo da aplicação, a saída é na forma digital (velocímetro e voltímetro) ou é necessário a conversão Digital/Analógico e um estágio de saída para atuação desta informação (alto-falante ou controle de um forno). Neste sistema, temos a utilização dos seguintes elementos:

a) Transdutor - Converte a variável física em elétrica. (microfone, termistor, fotosensor etc.);

b) Conversor A/D - Converte o sinal elétrico analógico em um número binário;

c) Circuito digital - Armazena ou processa a informação digital (número binário);

d) Decodificador para Display – Converte o número binário em decimal;

e) Conversor D/A - Converte a informação digital em sinal elétrico analógico;

f) Atuador – Amplifica ou controla a variável física através de um motor elétrico, por exemplo.

! 23 4 5

! 6

7 7

! 8

! 8 9 :;'

3 < ' %

=< 4 " % & 4; '

< '

$ >? < '

$ >? < ' 3

=< 4 % < ' " % &

'; :

4 : 4 : @ @ A

Figura 1.3 – Sistema genérico com conversores A/D e D/A.

2. Conversor Digital/Analógico (D/A)

Existem vários tipos de circuitos que realizam a conversão D/A e vários circuitos integrados dedicados para esta operação. Abordaremos, em nosso curso, os circuitos básicos.

2.1. Conversor D/A com amplificador operacional somador inversor.

No circuito da figura 2.1 temos um conversor com quatro bits de entrada (D, C, B e A) e a saída analógica (VOUT):

B

C(

C*

C, !

B

Obs.: MSB (Most Significant Bit) é o bit mais significativo e LSB (Least Significant Bit) é o bit menos significativo.

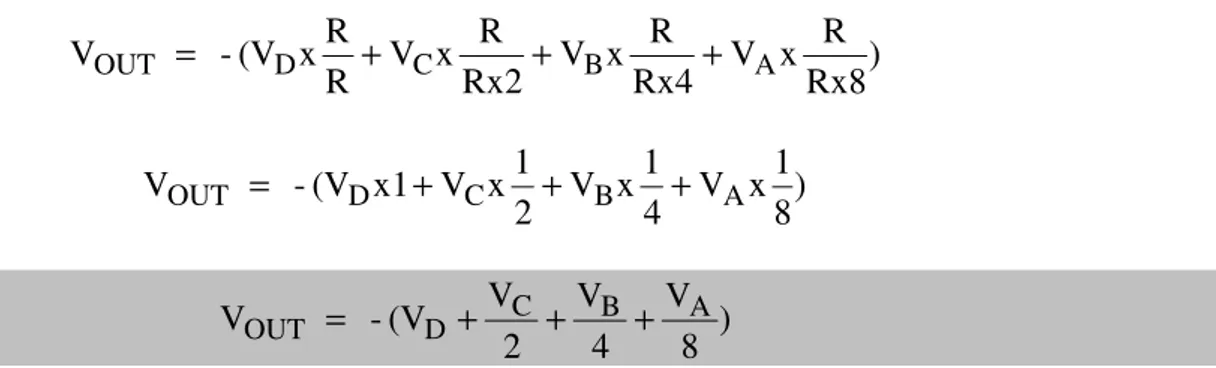

A equação da tensão de saída do circuito é:

) Rx8 R x V Rx4 R x V Rx2 R x V R R x (V

VOUT = D + C + B + A

) 8 1 x V 4 1 x V 2 1 x V x1 (V

VOUT = D + C + B + A

) 8 V 4 V 2 V (V

VOUT = D + C + B + A

As entradas D, C, B e A são binárias (0 ou 1). Considerando que para nível lógico “0” a tensão seja igual a 0V e que para nível lógico “1” a tensão seja igual a 5V, para o número binário DCBA = 1010 temos: B C( C* C, ! B B /! /! )! )!

Figura 2.2 – Conversor D/A com entrada DCBA = 1010.

) 8 V 4 V 2 V (V

VOUT = D+ C + B + A )

8 0 4 5 2 0 (5 + + +

= = -(5+0+1,25+0)

6,25V

V

OUT=

Na tabela a seguir temos os valores de VOUT de acordo com as entradas DCBA:

D C B A VOUT (volts)

0 0 0 0 0

0 0 0 1 -0,625

0 0 1 0 -1,250

0 0 1 1 -1,875

0 1 0 0 -2,500

0 1 0 1 -3,125

0 1 1 0 -3,750

0 1 1 1 -4,375

1 0 0 0 -5,000

1 0 0 1 -5,625

1 0 1 0 -6,250

1 0 1 1 -6,875

1 1 0 0 -7,500

1 1 0 1 -8,125

1 1 1 0 -8,750

1 1 1 1 -9,375

Tabela 2.1 – Tensão de saída em função das entradas DCBA.

Na tabela 2.1 foram consideradas tensões ideais de 5V aplicadas nas entradas DCBA, porém se estas entradas fossem conectadas às saídas de circuitos integrados da família TTL,por exemplo, teríamos tensões entre 2,4V e 4V para nível alto e tensões entre 0,35V e 0,5 para nível baixo. Se as entradas do conversor D/A forem conectadas diretamente às saídas de circuitos integrados a tensão na saída do conversor não será precisa. Para contornar este problema, utilizam-se as chaves bilaterais analógicas da família CMOS (CD4016 ou CD4066 entre outros existentes), conforme mostrado na figura 2.3:

B

C(

C*

C,

! B

B

3 D ' =< 4

4

'

E

F:

:

4

4

;

'

'

<

:

"@

'

G

@

@

G

4

'

:

'4

&

H/!

Figura 2.3 – Conversor D/A e interface com chave bilateral.

2.2. Conversor D/A com rede de resistores R/2R.

O circuito da figura 2.4 é mais prático porque é fácil obter apenas dois resistores com valores múltiplos de dois entre si.

B

3 D ' =< 4

, +

*

-0 /

.

( (

( (

F: !

! !

D

D I )

DH B

B

(

( DH I )I )!

Figura 2.4 – Conversor D/A com rede R/2R.

No circuito 2.5 temos as entradas DCBA = 1000:

I ) B

3 D ' =< 4

, +

*

-0 /

.

( (

( (

F: !

! !

D

D I ) DH

B I ) I ) I - B

(

( DH I )I )!

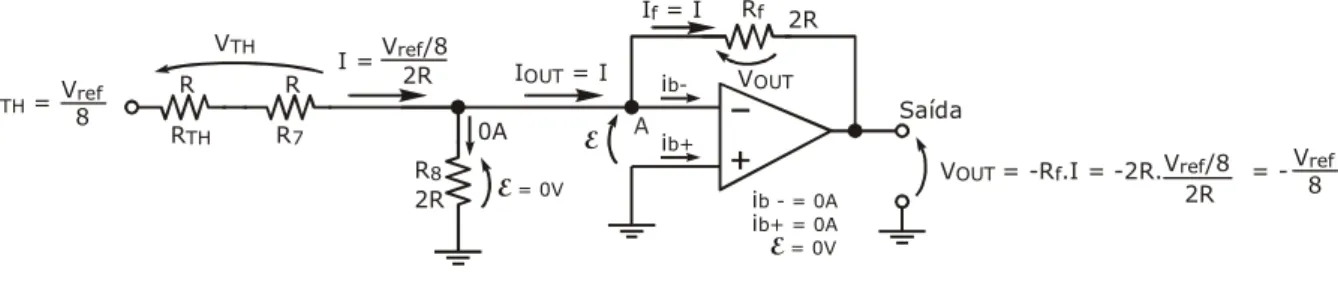

Na figura 2.6 (a) temos a simplificação do circuito 2.5. Na figura 2.6 (b), efetuado as associações dos resistores R1 a R7 temos a resistência equivalente (Req) que vale 2R. Como a entrada inversora do amplificador operacional é um terra virtual, a corrente do resistor R8 não passa pela resistência

equivalente (Req) e segue através de Rf. Para DCBA = 1000, a tensão de saída (VOUT) é igual à Vref.

,

0 /

.

(

F: !

! !

D

D I )

DH (

( DH I )

I )!

-(

* +

( (

(a) Circuito simplificado.

(

,

(

(

( F:

!

!

!

! I

! I I ( I !

!

D

D I )

DH

I

DH I ) I )!

I )! J

( I

(b) VOUT para DCBA = 1000.

Figura 2.6 – Simplificação do conversor D/A com entrada DCBA = 1000.

No circuito 2.7 temos as entradas DCBA = 0100:

I ) B

3 D ' =< 4

, +

*

-0 /

.

( (

( (

F: !

! !

D

D I )

DH B I )

I -I ) B

(

( DH I )I )!

Na figura 2.8(a) temos a simplificação do circuito 2.7. Na figura 2.8 (b), efetuado as associações dos resistores R1 a R5 temos a resistência equivalente (Req) que vale 2R. Na figura 2.8 (c), temos o gerador equivalente de Thevenin e a tensão de saída (VOUT).

, 0 /

.

(

(

F: !

! !

D

D I )

DH (

( DH I )

I )!

-(

*

+

(

(

(a) Circuito simplificado.

(

+

(

F: !

! !

J

! KI L

(

0

,

(

KI L

(b) Resistência equivalente (Req).

( ! (

(

! %(

!

I (

( F:

! %( I

! I I ( I

! ! K

D

D I ) DH

I

DH I ) I )! I )!

! KI 0

, ( K

)

(c) VOUT para DCBA = 0100.

No circuito 2.9 temos as entradas DCBA = 0010:

I ) B

3 D ' =< 4

, +

*

-0 /

.

( (

( (

F: !

! !

D

D I ) DH

B I -I ) I ) B

(

( DH I )I )!

Figura 2.9 – Conversor D/A com entrada DCBA = 0010.

Na figura 2.10(a) temos a simplificação do circuito 2.9. Na figura 2.10 (b), efetuado as associações dos resistores R1 a R3 temos a resistência equivalente (Req) que vale 2R. A figura 2.10 (c) mostra o gerador equivalente de Thevenin e a tensão de saída (VOUT).

, 0 /

.

(

(

F: !

! !

D

D I )

DH (

( DH I )

I )!

-(

+ *

( (

(a) Circuito simplificado.

(

F:

! !

J

! KI L

(

0 ,

(

KI L /

!

+ *

( (

* ! (

*

! %*

!

I (

( F:

! %* I

! I I ( I

! ! K

D

D I ) DH

I

DH I ) I )! I )!

! KI

0

, ( K

)

(c) VOUT para DCBA = 0010.

Figura 2.10 – Simplificação do conversor D/A com entrada DCBA = 0010.

No circuito 2.11 temos as entradas DCBA = 0001:

I - B

3 D ' =< 4

, +

*

-0 /

.

( (

( (

F: !

! !

D

D I )

DH B I )

I ) I ) B

(

( DH I )I )!

Figura 2.11 – Conversor D/A com entrada DCBA = 0001.

Na figura 2.12(a) temos a simplificação do circuito 2.11. A figura 2.12 (b) mostra o gerador equivalente de Thevenin e a tensão de saída (VOUT).

0

! K I L

/

(

F: !

!

(

(

K I L .

( ( , , ( F: !KI

! K ! %,

!

! ! %, I

! I I ( I

! D

D I ) DH

I

DH I ) I )! I )! , ( 0 K ) I

(b) VOUT para DCBA = 0001.

Figura 2.12 – Simplificação do conversor D/A com entrada DCBA = 0001.

Resumindo:

- Para DCBA = 1000

V

OUT=

-

V

ref- Para DCBA = 0100

2

V

V

OUT=

ref- Para DCBA = 0010

4

V

V

OUT=

ref- Para DCBA = 0001

8

V

V

OUT=

refAplicando o teorema da superposição de efeitos, temos a equação considerando as quatro entradas binárias (DCBA) aplicadas simultaneamente:

)

8

V

.

A

4

V

.

B

2

V

.

C

V

.

(D

V

OUT=

ref+

ref+

ref+

refAs entradas D, C, B e A são binárias (0 ou 1).

Exemplo – Considere Vref = 5V e calcule o valor da tensão de saída (VOUT) para DCBA = 1011 para o

conversor D/A com rede R/2R:

B

3 D ' =< 4 , + * -0 / . ( ( ( ( F: ! ! B B ( (

)

8

V

.

A

4

V

.

B

2

V

.

C

V

.

(D

V

OUT=

ref+

ref+

ref+

ref)

8

5

.

1

4

5

.

1

2

5

.

0

5

.

(1

V

OUT=

+

+

+

)

0,625

1,25

0

5

(

V

OUT=

+

+

+

,875

6

V

OUT=

2.3. Conversor D/A em circuito integrado (DAC08).

A seguir apresentaremos um dos circuitos integrados conversores D/A mais utilizados.

O DAC08 é um conversor de 8 bits, monolítico, de alta velocidade, saída em corrente e com um tempo de acomodação de aproximadamente 85ns.

Interface direta com as famílias: TTL, CMOS, ECL, HTL, PMOS. Deve-se ajustar o potencial VLC (pino 1) conforme a figura 2.15.

Descrição do terminais:

a) Terminal 1 - THRESHOLD CONTROL (VLC)

Através do terminal 1 é feito o ajuste para a interface com as famílias lógicas simplesmente por um ajuste adequado de tensão que é fornecido pelos fabricantes em manuais. O ajuste é feito utilizando a tensão threshold (VTH) de cada família. A tensão threshold (VTH) é igual a soma da tensão aplicada no terminal 1 (VLC) mais 1,4V correspondentes à queda de tensão nos dois diodos internos do circuito integrado.

VTH = VLC + 1,4

Figura 2.15 – Ajuste de VLC para outras famílias lógicas.

b) Terminal 2 – ( Iout ) e PINO 4 (Iout)

Duas saídas em correntes, complementares, que permitem a operação no modo diferencial para efetivamente dobrar a tensão de saída, com simples resistores de carga como mostra a figura 2.16.

A corrente de saída pode ser determinada pela seguinte expressão:

n REF O

2

A

x

I

I

=

onde:

IO - Corrente de saída em mA; IREF - Corrente de referência em mA;

A – Valor decimal equivalente à palavra binária aplicada na entrada digital; n - Número de bits

Exemplo:

Calcular a corrente de saída quando 10010111 é aplicado a entrada do DAC08 quando a corrente de referência é igual a 4 mA.

100101112 = 15110 A = 151

n = 8 bits

8 3 -n

REF O

2

151

x

4x10

2

A

x

I

I

=

=

mA

2,359

I

O=

c) Terminal 3 (V–) e terminal 13 (V+)

Terminais de alimentação do circuito integrado (± 4,5 V a ± 18 V).

d) Terminal 5 (B1) até o Terminal 12 (B8)

Entradas digitais, ligadas às saídas de circuitos integrados compatibilizada pela entrada VLC. A corrente

destas entradas são na ordem de 2 A.

e) Terminal 14 (VREF()) e Terminal 15(VREF())

Entradas para a corrente de referência (IREF) e ajustar a corrente de fundo de escala (IFS).

Na figura 2.17, temos:

REF REF REF

R V

Figura 2.17 – Operação básica com referência positiva para família TTL.

Corrente de fundo de escala:

256 255 x R

V I

REF REF FS

+ =

f) Terminal 16 (compensação).

Compensação em freqüência do amplificador operacional interno. Utiliza-se um capacitor (Cc) conectado entre este terminal e o terminal 3 (V–).

O valor deste capacitor depende da resistência ligada ao terminal 14 (R14 ou RREF). Para R14 igual a 1 k , 2,5 k ou 5 k , o valor mínimo do capacitor Cc é 15 pF, 37 pF ou 75 pF. Para outros valores de R14 deve-se utilizar a relação entre Cc (em pF) e R14 (em k ) igual a 15. Por exemplo, para R14 = 10 k o capacitor Cc é igual a 10 x 15 pF ou 150 pF. Desta forma o tempo de acomodação para variação de IREF = 0 para IREF = 2 mA será de 500 ns.

Exemplo - Na figura 2.18 temos o circuito para conversão unipolar positiva:

7I ($

B B

H-)!

/#Ω

/#Ω

/#Ω

-/! H-/!

)G)- 7µ -*

-/

/ -(

. -+ -. - (

*

a) Para valor de fundo de escala (11111111):

A = 255

mA 1,992 I 256 255 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O =

V 9,960 E 10 x 5 x 10 x 1,992 10 x 5 x I

EO = O 3 = -3 3 O=

b) Para valor de fundo de escala menos uma unidade (11111110):

A = 254

mA 1,984 I 256 254 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O =

V 9,922 E 10 x 5 x 10 x 1,984 10 x 5 x I

EO = O 3 = -3 3 O=

c) Para valor de meio de escala mais uma unidade (10000001):

A = 129

mA 1,008 I 256 129 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O =

V 5,039 E 10 x 5 x 10 x 1,008 10 x 5 x I

EO = O 3 = -3 3 O =

d) Para valor de meio de escala (10000000):

A = 128

mA 1,000 I 256 128 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O =

V 5,000 E 10 x 5 x 10 x 1,000 10 x 5 x I

e) Para valor de meio de escala menos uma unidade (01111111):

A = 127

mA 0,992 I 256 127 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O =

V 4,960 E 10 x 5 x 10 x 0,992 10 x 5 x I

EO = O 3 = -3 3 O =

f) Para o valor zero mais uma unidade (00000001):

A = 1

mA 0,0078 I 256 1 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O=

V 0,039 E 10 x 5 x 10 x 0,0078 10 x 5 x I

EO = O 3 = -3 3 O=

g) Para o valor zero (00000000):

A = 0

mA 0,000 I 256 0 x 10 x 2 256 A x 10 x 2

IO = -3 = -3 O =

V 0,000 E 10 x 5 x 10 x 0,000 10 x 5 x I

EO = O 3 = -3 3 O =

ENTRADA DIGITAL SAÍDA

MSB LSB IO (mA) EO (V)

Fundo de Escala 1 1 1 1 1 1 1 1 1,992 9,960

Fundo de Escala - LSB 1 1 1 1 1 1 1 0 1,984 9,922

Meio da Escala + LSB 1 0 0 0 0 0 0 1 1,008 5,039

Meio da Escala 1 0 0 0 0 0 0 0 1,000 5,000

Meio da Escala - LSB 0 1 1 1 1 1 1 1 0,992 4,960

Zero + LSB 0 0 0 0 0 0 0 1 0,0078 0,039

Zero 0 0 0 0 0 0 0 0 0,000 0,000

3

. Conversor Analógico/Digital (A/D)

A figura 3.1 ilustra um circuito básico para a conversão analógico/digital (A/D). Na entrada Vx é aplicada o sinal analógico e após o processamento obtêm-se o código binário correspondente.

"( H-&

!H

8

M "!C&

!

Figura 3.1 – Conversor A/D básico.

Funcionamento do circuito:

a) Aplica-se o sinal na entrada analógica (Vx);

b) A conversão inicia-se após a aplicação do pulso de “reset” no contador. Temos, neste momento, todas as saídas do contador iguais à zero;

c) Com todas as saídas do contador com valores iguais a zero aplicada à entrada do conversor D/A, a saída do conversor tem tensão igual a zero;

d) No comparador de tensão, a tensão na entrada positiva (+) é maior que a da entrada negativa (-) e com isto, temos nível alto na saída deste comparador de tensão e é aplicado à porta “E”; e) A porta “E” é uma chave digital controlada pelo nível lógico de saída do comparador de tensão.

Neste instante os pulsos de “clock” chegam ao contador;

f) A cada pulso de “clock”, o contador avança progressivamente a contagem binária e aplicada ao conversor D/A gera tensão que aumenta, também, gradativamente;

g) No instante em que a tensão na saída do conversor D/A ultrapassa o valor da tensão Vx, a saída do comparador muda para nível baixo, bloqueando os pulsos de clock para o contador. Neste momento temos na saída do contador, o código binário correspondente à tensão analógica Vx.

O intervalo entre cada pulso de “reset” deve ser tal que permita que o contador receba a quantidade de pulsos de “clock” necessário para que o contador chegue à contagem máxima. Para um sistema de oito bits são necessários 256 pulsos de “clock” para, a partir de 00000000, o contador atingir o valor

Na figura 3.2 temos a ilustração de funcionamento do circuito para diferentes valores de sinal analógico (Vx).

' " &

F: : 4 $@ :

: ' ?

' " & !C

F: : 4 3 % ' " & ' " & ": 4 ' : &

"4 ' : &

' " &

F: : 4 $@ :

: ' ?

' " & !C

F: : 4 3 % ' " & ' " & ": 4 ' : &

"4 ' : &

(b) (c)

' " &

F: : 4 $@ :

: ' ?

' " & !C

F: : 4 3 %

' " & ' " & ": 4 ' : &

"4 ' : &

(a)

4. Parâmetros dos conversores.

4.1. Freqüência de amostragem.

A freqüência da amostragem (freqüência de Nyquist) deve ser maior ou igual a duas vezes a maior freqüência do sinal analógico, assim reduz-se o risco de perda de informações importantes.

=< 4

'

$ ' < $

'

Figura 4.1 – Amostragem.

4.2. Resolução (fração de variação).

É a menor variação possível nos conversores. No conversor D/A é a menor variação obtida na saída analógica e no conversor A/D corresponde à variação de um bit no dígito menos significativo.

!

! "!&

3 < ' %

=< 4 " % & ' :

B 2

3 < ' %

=< 4 " % & 4#

0 1 ---.

-/ 7; : :4

----4.3. Fundo de escala.

É o maior valor possível que se pode obter na saída de um conversor. Na figura 4.2 note que para quatro bits o maior número binário é 1111, que corresponde à tensão analógica de 15V (valor de fundo de escala).

4.4. Tempo de conversão.

Nos conversores A/D corresponde ao tempo necessário para o circuito completar a conversão da informação analógica em digital. Quanto menor for o tempo de conversão mais amostragens podem ser obtidas, num mesmo intervalo de tempo, e melhor será a precisão do circuito.

"( H-&

!H

8

M "!C&

!

Figura 4.3 – Conversor A/D.

' " &

F: : 4 $@ :

: ' ?

' " & !C

F: : 4 3 %

! 6

' " & ' " & ": 4 ' : &

4.5. Tempo de Acomodação.

Quando ocorre variação de uma tensão contínua existirá a oscilação desta tensão até esta se acomodar ao valor final. Esta oscilação ocorre devido às capacitâncias, parasitas ou do circuito. Esta oscilação é mostrada na figura 4.5.

'

!

7 (N

$@ : 4 $ : >?

Figura 4.5 – Tempo de acomodação.

Nos conversores em geral o tempo de acomodação, para valores com variação inferiores a ±2% do