ESCOLA SUPERIOR DE TECNOLOGIA

UNIVERSIDADE DO ESTADO DO AMAZONAS

SISTEMAS DIGITAIS II

Professor Paulo Cesar de Souza Cavalcante

SUMÁRIO

ASSUNTO PÁG.

CAPÍTULO 1 – RECAPITUALAÇÃO ALGEBRA BOOLEANA 1

1 CIRCUITOS LÓGICOS ... 1

2 TEOREMAS DA ÁLGEBRA BOOLENA ... 3

3 FÓRMULA DE INTERPOLAÇÃO DE LAGRANGE ... 6

4 MAPA DE KARNAUGH ... 8

SIMPLIFICAÇÃO DE CIRCUITOS LÓGICOS ... 8

COMPLEMENTAÇÃO PELO MÉTODO DOS MAPAS ... 10

MÉTODO DE ATAQUE PARA LEITURA DE MAPAS ... 11

CAPÍTULO 2 – DISPOSITIVOS DE MEMÓRIA 13 1 CIRCUITO FLIP-FLOP ... 13

2 FLIP-FLOP SR ... 13

FLIP-FLOP SR COM PORTAS NOR ... 13

FLIP-FLOP SR COM PORTAS NAND ... 16

FLIP-FLOP SR COM CLOCK ... 18

3 FLIP-FLOP TIPO T ... 20

4 FLIP-FLOP TIPO JK ... 21

FLIP-FLOP JK COM CLOCK ……… 22

5 FLIP-FLOP TIPO D ... 24

LATCH D (LATCH TRANSPARENTE) ... 25

ENTRADAS SÍNCRONAS E ASSÍNCRONAS ... 26

6 TEMPORIZAÇÃO DE FLIP-FLOPS ... 28

7 FLIP-FLOP MESTRE-ESCRAVO ... 29

CAPÍTULO 3 – CIRCUITOS CONTADORES 31 REVISÃO DE CÓDIGOS BINÁRIO-DECIMAL ... 31

1 CONTADORES ASSÍNCRONOS ... 32

CONTADORES DIRETOS E INVERSOS ... 32

CONTADOR ASSÍNCRONO DIRETO (CONTADOR UP) ... 33

CONTADOR ASSÍNCRONO INVERSO (CONTADOR DOWN) ... 33

MÓDULO DE UM CONTADOR ... 34

CIRCUITOS DIVISORES POR N ... 35

DECODIFICAÇÃO DE CONTAGENS ESPECÍFICAS ... 36

CIRCUITOS INTEGRADOS DE CONTADORES ASSÍNCRONOS ... 37

ASSUNTO PÁG.

2 CONTADORES SÍNCRONOS OU PARALELOS ... 38

TEMPORIZAÇÃO DE CIRCUITOS CONTADORES ... 39

CONTADORES COM CARGA PARALELA ... 40

PROJETO DE CONTADOR SÍNCRONO ... 40

PROJETO DE CONTADOR SÍNCRONO BIDIRECIONAL (UP-DOWN) ... 45

CONTADOR SÍNCRONO DE MÓDULO 8 UP/DOWN ... 47

CONTAGENS IRREGULARES E TRUNCADAS ... 49

PROJETO DE CONTADOR SÍNCRONO UTILIZANDO FF TIPO D ... 49

CIRCUITOS INTEGRADOS DE CONTADORES SÍNCRONOS ... 50

CONTADOR DE MÓDULO VARIÁVEL UTILIZANDO CI 74LS193 ... 52

ASSOCIAÇÃO DE CIs CONTADORES SÍNCRONOS ... 54

CAPÍTULO 4 – CIRCUITOS MULTIVIBRADORES 55 1 CIRCUITOS MULTIVIBRADORES MONOESTÁVEIS ... 55

MONOESTÁVEL NÃO-REDISPARÁVEL ... 56

MONOESTÁVEL REDISPARÁVEL ... 57

DISPOSITIVOS SCHMITT-TRIGGER ... 57

CIRCUITOS INTEGRADOS DE MULTIVIBRADORES MONOESTÁVEIS .... 58

APLICAÇÕES DE CIs MULTIVIBRADORES MONOESTÁVEIS ... 59

2 CIRCUITOS MULTIVIBRADORES ASTÁVEIS ... 60

OSCILADOR SCHMITT-TRIGGER ... 60

CI TEMPORIZADOR 555 USADO COMO MULTIVIBRADOR ASTÁVEL ... 61

3 APLICAÇÕES DE CONTADORES E MULTIVIBRADORES EM SISTEMAS DIGITAIS ... 63 RELÓGIO DIGITAL ... 63

FREQUENCÍMETRO ... 65

CAPÍTULO 5 – CIRCUITOS REGISTRADORES DE DESLOCAMENTO 68 1 REGISTRADORES DE DESLOCAMENTO COM FFs JK ... 68

2 REGISTRADORES DE DESLOCAMENTO COM FFs D ... 69

3 CONTADORES COM REGISTRADORES DE DESLOCAMENTO ... 69

CONTADOR EM ANEL ... 70

CONTADOR JOHNSON ... 71

DECODIFICANDO AS SAÍDAS DE UM CONTADOR JOHNSON ... 72

4 CIRCUITOS INTEGRADOS DE REGISTRADORES ... 73

CIs DE ENTRADA PARALELA/SAÍDA PARALELA ... 73

CIs DE ENTRADA SERIAL/SAÍDA SERIAL ... 76

CIs DE ENTRADA PARALELA/SAÍDA SERIAL ... 77

CIs DE ENTRADA SERIAL/SAÍDA PARALELAV ... 78

ASSUNTO PÁG.

CAPÍTULO 6 – CIRCUITOS DE MEMÓRIA 80

1 TERMINOLOGIA DE MEMÓRIAS ... 80

2 OPERAÇÃO DE MEMÓRIAS ... 81

3 MÉMORIAS SOMENTE DE LEITURA ... 83

ARQUITETURA DE UMA ROM ... 84

ROM PROGRAMADA POR MÁSCARA ... 85

ROM PROGRAMÁVEL (PROM) ... 86

ROM PROGRAMÁVEL E APAGÁVEL (EPROM)... 87

MEMÓRIA FLASH ... 89

4 MÉMORIAS DE LEITURA E DE ESCRITA ... 90

ARQUITETURA DE UMA RAM ... 90

RAM ESTÁTICA (SRAM)... 91

RAM DINÂMICA (DRAM) ... 92

5 BANCOS DE MEMÓRIA ... 96

CAPÍTULO 7 – CIRCUITOS LÓGICOS PROGRAMÁVEIS 99 1 DISPOSITIVOS LÓGICOS PROGRAMÁVEIS (PLD) ... 99

2 HARDWARE DO ARRANJO LÓGICO GENÉRICO (GAL) ... 99

MACRO CÉLULA DA LÓGICA DE SAÍDA ... 101

MODOS DE CONFIGURAÇÃO ... 103

3 PROGRAMAÇÃO DE PLD ... 107

SOFTWARE DE DESENVOLVIMENTO ... 108

COMPILADOR UNIVERSAL PARA LÓGICA PROGRAMÁVEL ... 108

CICLO DE DESENVOLVIMENTO DO PROJETO ... 110

CAPÍTULO 8 –

CIRCUITOS CONVERSORES A/D E D/A

113 1 INTERFACE ANÁLOGICA-DIGITAL-ANALÓGICA ... 1132 CONVERSORES DIGITAIS-ANALÓGICOS (D/A) ... 114

CARACTERÍSTICAS DE CONVERSORES D/A ... 114

3 CIRCUITOS CONVERSORES D/A ... 117

CONVERSOR D/A COM AMPLIFICADOR SOMADOR ... 117

CONVERSOR D/A COM SAÍDA EM CORRENTE ... 118

CONVERSOR D/A COM RESISTORES R/2R ... 118

4 CIRCUITOS INTEGRADOS DE CONVERSORES D/A ... 119

5 CONVERSORES ANALÓGICO-DIGITAIS (A/D) ... 120

6 CIRCUITOS CONVERSORES D/A ... 121

CONVERSOR A/D DE RAMPA DIGITAL ... 121

CONVERSOR A/D DE APROXIMAÇÃO SUCESSIVA ... 123

CONVERSOR A/D FLASH ... 124

7 CARACTERÍSTICAS DE CONVERSORES D/A ... 126

CAPÍTULO 1

RECAPITULAÇÃO DE ALGEBRA BOOLEANA

1) CIRCUITOS LÓGICOS

CIRCUITO E (AND)

A saída só será alta se todas as entradas forem altas.

Simbologia Tabela Verdade

Em LP

Expressão Lógica

A B S S =A.B

0 0 0

0 1 0

1 1 1

1 0 0

CIRCUITO OU (OR)

A saída só será baixa se todas as entradas forem baixas.

Simbologia Tabela Verdade

Em LP

Expressão Lógica

A B S S = A + B

0 0 0

0 1 1

1 1 1

1 0 1

CIRCUITO NÃO (NOT)

A saída será baixa se a entrada for alta e será alta se a entrada for baixa.

Simbologia Tabela Verdade

em LP

Expressão Lógica

A S S=A

0 1

CIRCUITO NÃO-E (NAND)

A saída só será baixa se todas as entradas forem altas.

Simbologia Tabela Verdade

em LP

Expressão Lógica

A B S S=A.B

0 0 1

0 1 1

1 1 0

1 0 1

CIRCUITO NÃO-OU (NOR)

A saída só será alta se todas as entradas forem baixas.

CIRCUITO OU-EXCLUSIVO (XOR)

A saída será alta somente quando suas duas entradas forem diferentes (Porta da desigualdade).

CIRCUITO NÃO OU-EXCLUSIVO (XNOR)

A saída será alta somente quando suas duas entradas forem iguais (Porta da igualdade).

Simbologia Tabela Verdade

em LP

Expressão Lógica

A B S S=A+B

0 0 1

0 1 0

1 1 0

1 0 0

Simbologia Tabela Verdade

em LP

Expressão Lógica

A B S S=A⊕B

0 0 0

0 1 1

1 1 0

A

B

S

2) TEOREMAS DA ÁLGEBRA BOOLEANA

Os teoremas que serão abordados a seguir são utilizados para simplificação de expressões lógicas e para obtenção de expressões equivalentes.

1a) 0.X=0 1b) 1+X=1

2a) 1.X=X 2b) 0+X=X

3a) X.X=X 3b) X+X=X

4a) X. X =0 4b) X+ X =1

5a) X.Y=Y.Z 5b) X+Y=Y+Z

6a) X.Y.Z= X.(Y.Z)=(X.Y).Z 6b) X+Y+Z= X+(Y+Z)=(X+Y)+Z

7a) XY...Z=X+Y+...+Z 7b) X+Y+...+Z=X.Y.....Z

8) f(X,Y,...,Z,.,+)=f(X,Y,...,Z,+,.)

9a) X.Y+X.Z=X(Y+Z) 9b) (X+Y).(X+Z)=X+(Y.Z)

10ª) X.Y+X Y =X 10b) (X+Y).(X+ Y )=X

11ª) X+X.Y=X 11b) X.(X+Y)=X

12ª) X+ X Y=X+Y 12b) X.( X +Y)=X.Y

13ª) Z.X+Z. X .Y=Z.X+Z.Y 13b) (Z+X).(Z+ X +Y)=(Z+X).(Z+Y)

14ª) X.Y+ X .Z+Y.Z= X.Y+ X .Z 14b) (X+Y).( X +Z).(Y+Z)=(X+Y).( X +Z)

Simbologia Tabela Verdade

em LP

Expressão Lógica

A B S S=A⊗B

0 0 1

0 1 0

1 1 1

A

B

S

15ª) X.Y+ X .Z=(X+Z).( X +Y) 15b) (X+Y).( X +Z)=X.Z+ X .Y

16ª) X.f(X, X ,Y,...,Z)=X.f(1,0,Y,...,Z) 16b) X+f(X, X ,Y,...,Z)=X+f(0,1,Y,...,Z)

Observações:

a) O teorema 16a) estabelece que se uma variável X é multiplicada por uma expressão contendo ocorrências e X e X , então todos os X na expressão podem ser substituídos por 1, e todos X por 0. Isto é permitido porque : X.X=X.1=X e X. X =X.0=0.

Exemplo:

B[ B (A+C)+B A +B( A + B CD)]= B[0(A+C)+1 A +1( A +0CD)]= B[0+ A + ( A )]=

B[ A + A ]= B[ A ]=B A

b) O teorema 16b) estabelece que se uma variável X é somada a uma expressão contendo ocorrências de X e X , então todos os X na expressão podem ser substituídos por 0, e todos

X por 1. Isto é permitido porque: X+X=X+0=X e X+ X =X+1=1.

Exemplo:

X+ X A+ AX + X DU+XAD= X+[ X A+XA+ X DU+XAD]= X+[1A+1 A +1DU+0AD]= X+[A+ A +DU]=

X+[1+DU]= X+1=1

Como exemplo da utilização da tabela verdade para comprovação de teorema, executaremos a demonstração para os teoremas 14a) e 14b). Este método consiste em mostrar a validade do teorema para todas as possíveis combinações dos valores das variáveis envolvidas. No caso da álgebra de Boole, é possível determinar o número de possíveis combinações através da fórmula K=2n, onde k é o número de combinações procurado, 2 são os possíveis valores das variáveis (0 e 1) e n é o número de variáveis envolvidas.

O teorema terá sido demonstrado se para todas as combinações possíveis das variáveis, as duas expressões ligadas pela igualdade apresentarem o mesmo resultado. Isto atende o conceito de expressões equivalentes, portanto as duas expressões são equivalentes.

Variáveis X Y Z

Expressão XY+X Z+YZ

Expressão Equivalente XY+X Z

0 0 0 0 0

0 0 1 1 1

0 1 1 1 1

0 1 0 0 0

1 1 0 1 1

1 1 1 1 1

1 0 1 0 0

1 0 0 0 0

O teorema 14b) é o dual do teorema 14a), portanto para demonstra-lo basta fazer o dual da tabela verdade anterior, ou seja, os valores 0 na tabela serão substituídos pelo seu dual 1 e vice-versa.

Para o teorema 14b) (X+Y)( X +Z)(Y+Z)=(X+Y)( X +Z), a tabela verdade que demonstra a validade do teorema será:

Variáveis X Y Z

Expressão (X+Y).( X +Z).(Y+Z)

Expressão Equivalente (X+Y).( X +Z)

1 1 1 1 1

1 1 0 0 0

1 0 0 0 0

1 0 1 1 1

0 0 1 0 0

0 0 0 0 0

0 1 0 1 1

0 1 1 1 1

Observações:

a) Nos teoremas 14a) e 14b) respectivamente, os termos YZ e Y+Z são comumente chamados de termos fantasmas, pois pode-se constatar que no segundo lado da igualdade das expressões dos teoremas estes termos simplesmente desaparecem sem nada alterar, ou por outra, simplesmente aparecem no primeiro lado da igualdade sem também nada alterar.

b) O teorema 8) é conhecido com Teorema de DeMorgan que diz:

“O complemento de uma função f pode ser obtida da seguinte forma: substituindo-se cada variável por seu complemento e todos os conectivos E por OU e vice-versa.”

Exemplo:

Simplificar as seguintes expressões:

=AB+ABD+ABC+ABD= B(A+AD)+ABC+ABD= BA+BD+ABC+ABD=

=BA+D(B+AD)+ABC= BA+DB+DA+ABC= A(B+BC)+DB+DA= =AB+DB+DA+AC=

(Aqui notar que BD é o termo fantasma da expressão AB+DB+DA) =AB+DA+AC

b) CDF+CDF+CDF+CDF

=C(DF+DF)+CDF+CDF= CD+CDF+CDF=

=CD+(CDF+CDF)=CD+CD=C

c) BCD+BDE+BCD+CE+DE

=BCD+BDE+BCD+CE+DE= BCD+D(BE+E)+BCD+CE= =BCD+DB+DE+BCD+CE=BCD+DB+DE+BCD+CE=

=BCD+D(B+BC)+DE+CE=

=BCD+D(B+BC)+DE+CE= BCD+DB+DC+DE+CE=

=BCD+DB+DC+DE+CE=

(Aqui notar que CDé o termo fantasma da expressão DC+DE+CE) =BCD+DB+DE+CE= DB(C+1)+DE+CE=

=DB+DE+CE=

3) FÓRMULA DE INTERPOLAÇÃO DE LAGRANGE

Esta fórmula é uma ferramenta muito útil na solução de problemas lógicos, e será aplicada em circuitos lógicos seguindo o seguinte Teorema:

“Qualquer função de n variáveis, cada uma das quais assumindo somente um dos dois valores lógicos 0 ou 1, e a própria função também assumindo de cada vez um dos dois valores lógicos 0 ou 1, é igual ao polinômio dado pela fórmula de interpolação de Lagrange”.

Isto é:

F(X,Y,...,Z)=f(0,0,...,0).X.Y...Z +f(0,0,...,1).X.Y...Z+ ... +f(0,1,...,0). X.Y...Z+f(1,0,...,0). X.Y...Z

Exemplos:

a) Para n=1 (uma variável), número de combinações é 2n=21=2, achar a expressão f(X).

X f(X) f(X)=f(0). X + f(1).X

b) Para n=2 (duas variáveis), número de combinações é 2n=22=4, achar a expressão f(X,Y).

XY f(X,Y) f(X,Y)=f(0,0).XY+ f(0,1). YX + f(1,1).XY+ f(1,0). YX 00 f(0,0)

01 f(0,1) 11 f(1,1) 10 f(1,0)

b) Achar a expressão Boolena da função lógica definida na tabela de valores.

XY f(X,Y) f(X,Y)=f(0,0).XY+ f(0,1). YX + f(1,1).XY+ f(1,0). YX 00 0 f(X,Y)=0. YX + 1. X + 1.XY+ 1. YY X

01 1 f(X,Y)= YX + XY+XY

11 1 f(X,Y)=Y(X+X)+XY=Y+XY

10 1 f(X,Y)=X+Y

A expressão lógica expressa pela tabela é a função lógica OU entre duas variáveis.

c) Achar a expressão Boolena da função lógica definida na tabela de valores.

XY f(X,Y) f(X,Y)=f(0,0).XY+ f(0,1). YX + f(1,1).XY+ f(1,0). YX 00 0 f(X,Y)= YX + XY=Y(X+X)

01 1 f(X,Y)=Y

11 1

10 0

A expressão lógica expressa pela tabela é a função lógica OU entre duas variáveis.

d) Achar a expressão Boolena da função lógica definida na tabela de valores.

Esta tabela já foi apresentada no exemplo c), entretanto observa-se que a quantidade de valores de resultado da função igual a 0 é muito menor que igual a 1. Desta forma, torna-se mais prático retirar o valor da expressão “por zeros”. Tirando-se “por zero” pode-se tomar o valor do complemento da função f e depois complementa-la a fim de obter a expressão da função. Esta solução está expressa abaixo:

XY f(X,Y) f(X,Y)= f(0,0) .XY+ f(0,1) .X + f(1,1) .XY+ f(1,0) Y XY

00 0 f(X,Y)=1.XY+ 0. X + 0.XY+ 0.Y XY

01 1 f(X,Y)=XY

11 1 f(X,Y)= YX

10 1 f(X,Y)=X+Y

XYZ f(X,Y,Z) f (X,Y,Z)=XY +XYZ Z

000 1 f(X,Y,Z)=XYZ+XYZ

001 0 f(X,Y,Z)= XYZ.XYZ

011 1 f(X,Y,Z)= (X+Y+Z).(X+Y+Z)

010 1 110 1 111 0 101 1 100 1

4) MAPA DE KARNAUGH

SIMPLIFICAÇÃO DE CIRCUITOS LÓGICOS

O Mapa de Karnaugh é método destinado a simplificação de expressões lógicas, através da aplicação da seguinte metodologia.

a) Um mapa de n variáveis contém 2n quadrados.

b) Um 1 é assinalado em cada quadrado representando um combinação de entrada para qual uma saída é desejada.

c) Um 0 é colocado em cada quadrado representando uma combinação para a qual nenhuma saída é desejada.

d) Um traço é colocado no quadrado correspondente a uma combinação denominada opcional. e) Em se lendo um mapa, dois quadrados 1 que são adjacentes podem ser agrupados

horizontalmente ou verticalmente.

f) São adjacentes horizontalmente e verticalmente os quadrados que diferirem em somente uma variável respectivamente.

g) O número de quadrados agrupados devem ser sempre potências de 2.

h) As variáveis que são constantes para um determinado agrupamento de quadros 1 definem o grupo.

i) Todo quadrado 1 deve ser computado no mínimo uma vez, embora um quadrado 1 possa ser usado em tantos grupos quanto desejado.

j) Um grupo deve ser tão grande quanto possível, isto é, um quadrado 1 não será computado por ele mesmo se puder ser computado num grupo de dois quadrados 1. Um grupo de dois quadrados 1 não seria formado se os quadrados 1 que comporiam este grupo pudessem ser incluídos num grupo de quatro quadrados 1, e assim por diante.

k) Todos os quadrados 1 serão computados para o mínimo número de grupos, e a expressão resultante lida no mapa será a mínima soma de produtos, isto é, a expressão mais simplificada.

Exemplos: Dados os mapas retirar as expressões lógicas definidas pelos mesmos:

a) AB 00 01 11 10

b) AB 00 01 11 10

1 1 S=A

c) AB 00 01 11 10

1 1 S=B

d) AB 00 01 11 10

1 1 S=AB+AB

e) AB

C 00 01 11 10

0 1 S=AB

1 1

f) AB

C 00 01 11 10

0 1 1 S=B+C

1 1 1 1 1

g) AB

C 00 01 11 10

0 1 1 S=AB+BC

1 1

h) AB

C 00 01 11 10

0 S=BC+AC

1 1 1 1

i) AB

C 00 01 11 10

0 1 1 S=BC+AB

1 1

j) AB

C 00 01 11 10

0 1 1 S=B

1 1 1

k) AB

CD 00 01 11 10

00 1 1 S=AD

11

10 1 1

l) AB

CD 00 01 11 10

00 1 1 S=BD

01 11

10 1 1

m) AB

CD 00 01 11 10

00 1 1 S=B

01 1 1

11 1 1

10 1 1

n) AB

CD 00 01 11 10

00 1 1 1 1 S=D

01 11

10 1 1 1 1

o) ABC

DE 000 001 011 010 110 111 101 100

00

01 1 1 S=BCDE+BCDE

11

10 1 1

COMPLEMENTAÇÃO PELO MÉTODO DOS MAPAS

É possível complementar uma expressão lógica através dos mapas. Na complementação, os quadrados 0 são agrupados ao invés dos quadrados 1. Os agrupamentos de quadrados 0 definem a expressão complementada.

Exemplos: Achar a expressão e a expressão complementada definidas pelos mapas abaixo:

a) AB

C 00 01 11 10

0 0 0 0 0 S=C e S=C

b) AB

C 00 01 11 10

0 0 1 1 0 S=B+C e S=BC

1 1 1 1 1

MÉTODO DE ATAQUE PARA LEITURA DE MAPAS

Uma boa aproximação da leitura da solução ótima de um Mapa de Karnaugh é a seguinte:

1º) Olha-se primeiro para quaisquer quadrados 1 que não combinam com quaisquer outros, estas entradas devem ser computadas por elas próprias.

2º) Olha-se em seguida para qualquer quadrado 1 que combina com somente um outro quadrado 1. Estes grupos devem ser assim computados.

3º) Olha-se então para um quadrado 1 que combina com exatamente dois outros quadrados 1, verifica-se verifica-se há um quarto quadrado 1 que combina com estes trêspara formar um grupo de quatro:

a) se houver um quarto quadrado, a saída será computada como um grupo de quatro, b) se não houver, haverá um escolha que deverá ser deixada para o fim.

Exemplos:

a) AB

C 00 01 11 10

0 1 1 1 S=AB+BC

1 1

b) AB

CD 00 01 11 10

00 1 1 1 S=BCD+ABD+ABD+BCD

01 1 1 1

11 1

10 1

Observação:

Exercícios:

Simplificar as expressões abaixo, utilizando o Mapa de Karnaugh.

a) S=ABC+ABC+ABC+ABC

AB

C 00 01 11 10

0 1 S=AB+BC+AC

1 1 1 1

b) S=BC+AB+BC+AC+C

AB

C 00 01 11 10

0 1 1 S=B+C

1 1 1 1 1

c) S=ABC+ABC+ABC+ABC

AB

C 00 01 11 10

0 S=C

1 1 1 1 1

d) S=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

AB

CD 00 01 11 10

00 1 1 S=BCD+CD

01

11 1 1 1 1

10

Achar a expressão booleana mais simplificada definida pela tabela abaixo, utilizando o Mapa de Karnaugh:

A B C S AB

0 0 0 0 C 00 01 11 10

0 0 1 1 0 1 1 1

0 1 0 1 1 1

0 1 1 0

1 1 1 0 S=ABC+BC+AC

1 1 0 1

1 0 1 0

CAPÍTULO 2

DISPOSITIVOS DE MEMÓRIA

Em muitas aplicações lógicas, exige-se que as saídas de determinados circuitos sejam mantidas por tempo indefinido, ou seja, que seja memorizado. A função de circuitos de memória pode ser executada por diversos dispositivos. Os mais comumente utilizados são os circuitos denominados Flip-Flop.

1) CIRCUITO FLIP-FLOP

O Flip-Flop, ou elemento biestável, tem dois estados estáveis de operação, que correspondem aos níveis lógicos 0 e 1. A saída muda de um estado para outro em função da entrada.

O Flip-Flop pode ser definido como um dispositivo que guarda informação binária na forma de 0 e 1, e pode ser mantido indefinidamente em qualquer dos dois estado, podendo também ser chaveado de um estado para outro.

Os tipos de Flip-Flop a serem vistos neste estudo são:

• Flip-Flop SR

• Flip-Flop T

• Flip-Flop JK

• Flip-Flop D

2) FLIP-FLOP SR

FLIP-FLOP SR COM PORTAS NOR

O Flip-Flop SR tem duas linhas de entradas S ou “SET” e R ou “RESET”, e duas saídas Q e Q . A

entrada S liga a saída Q para o estado 1, e a saída Q para 0, e a entrada R desliga a saída Q para o

estado 0, e a saída Q para o estado 1.

Denominando-se Q a saída antes da aplicação das entradas S e R, e Qf a saída após a atuação das entradas após a atuação das entradas S e R, a Tabela verdade para o Flip-Flop está representada a seguir.

Tabela Verdade do Flip-Flop SR

Entradas Saídas

S R Q Qf

0 0 0 0 0 0 1 1 0 1 1 0 0 1 0 0 1 1 0 - 1 1 1 - 1 0 1 1 1 0 0 1

Retirando-se a expressão das saídas Q e fQ por Lagrange, tem-se:

Q R S Q R S SRQ Q SR Q R S

Qf = + + + +

Q R S ) Q R Q R RQ Q R ( S

Qf = + + + +

Q R S S Q R S ) R R ( S

Qf = + + = +

Q R S Qf = +

SRQ Q SR Q R S RQ S Q R S f

Q = + + + +

) Q Q R ( S ) Q R RQ Q R ( S f

Q = + + + +

SR R S Q S SR ) R Q ( S f

Q = + + = + +

R Q S f

Q = +

Para obtenção do circuito utilizando-se somente portas lógicas NÃO-OU obteremos as expressões abaixo: Q R S Q R S Q R S

Qf = + = + = + +

R Q S R Q S R Q S f

Q = + = + = + +

Circuito da Saída Q Saídas das Portas Lógicas Q R S 1

S = + +

Q Q R S 2

S = + + =

Q 3 S = S R 1 2 3 4 Q R Q 4

S = +

Circuito da Saída Q Saídas das Portas

Lógicas

Q S 5

S = +

Q S R 6

S = + +

Q Q S R 7

S = + + = S

R

5 6 7

8 _ Q Q 8 S =

Dos circuitos acima observa-se que os blocos 1 e 5 geram Q e os blocos 4 e 6 geram Q. O circuito mais simplificado do Flip-Flop SR implementado com portas NOR, tabela verdade e simbologia estão abaixo representados em (a), (b) e (c), respectivamente.

Abaixo está representada a carta de tempo para oFF SR implementado com portas NOR.

FLIP-FLOP SR COM PORTAS NAND

De maneira análoga à anterior, pode-se implementar a função lógica do Flip-Flop SR utilizando-se somente blocos lógicos NÃO-E.

Q R . S Q R S Q R S

Qf = + = + =

R . Q S R Q S R Q S f

Q = + = + =

Implementado-se as expressões tem-se o seguinte circuito:

S

R

Q

_ Q

_ S

_ R

Q

_ Q

O circuito mais simplificado do Flip-Flop SR implementado com portas NAND, sua tabela verdade e simbologia estão a seguir representados em (a), (b) e (c) respectivamente.

FLIP-FLOP SR COM CLOCK

Este Flip-Flop é idêntico ao FF SR no que diz respeito à lógica de funcionamento e tabela verdade. Porém, as informações de entrada somente são transferidas ao FF quando na entrada CLOCK ou GATE ou STROBE houver um nível lógico 1. Os termos GATED, STROBED e SYNCHRONOUS são frequentemente utilizados em substituição a CLOCKED na designação deste tipo de FF.

Na figura abaixo, as funções NAND desempenhadas pelas portas OR de números 3 e 4, constituem o FF SR ou SC já visto anteriormente. As portas NAND de números 1 e 2 só permitem que os níveis de entrada aplicados na entrada SET e CLEAR sejam entregues ao FF SC quando houver um nível 1 em cada uma das outras entradas de cada porta NAND.

O circuito Detector de transição possibilita que ao invés de dar-se a permissão de acesso ãs entradas SC por nível lógico 1, essa permissão seja dada por transição do nível de tensão do sinal de clock. Há duas possíveis transições de sinal, a positiva ou borda de subida do pulso e a negativa ou borda de descida do pulso de clock.

Na figura abaixo estão representados a simbologia do Flip-Flop SR ou SC disparado na transição positiva, a tabela verdade e a carta de tempo desse FF, respectivamente em (a), (b) e (c).

3) FLIP-FLOP TIPO T

O Flip-Flop tipo T ou Toggle FF muda de estado após um pulso na entrada T (Trigger) ou Clock. A sua tabela verdade é representada abaixo, sendo QA a saída Q antes da atuação do clock e Q a mesma saída

Q após atuação do pulso de clock.

Entrada T Saída QA Saída Q

0 0 0 0 1 1 1 1 0 1 0 1

Pelo exame da tabela verifica-se que antes da aplicação do pulso de clock Q=QA. Após a aplicação do

clock Q=QA, ou seja, que houve uma mudança de estado da saída Q.

Para implementação do circuito do Flip-Flop tipo T, será utilizado o FF SR com portas NAND já visto anteriormente. A tabela verdade abaixo relaciona a nova entrada T, o estado atual da saída Q, ou seja QA, e os níveis de saída necessários ao FF RS para implementação da função T, ou função de

comutação.

Ent T

Saída QA

anterior atuação T Saída Q posterior atuação T Ent S Ent R

0 0 0 1 1

0 1 1 1 1

1 0 1 0 1

1 1 0 1 0

Retirando-se as expressões da tabela tem-se que : S =TQA e R=TQA.

Implementando-se o circuito do Flip-Flop tipo T tem-se:

_ S _ R Q _ Q T

T

Q

Q

Pode-se observar que para dois períodos do sinal T (clock) há um período do sinal de saída Q, ou seja, o FF tipo T pode ser utilizado para realizar a divisão de freqüência do sinal de clock por 2.

4) FLIP-FLOP TIPO JK

O Flip-Flop JK tem duas linhas de entrada, linha J com efeito similar ao da linha S do FF SR, e linha K com efeito similar ao da linha R do FF SR. A grande diferença entre o FF JK e o FF SR diz respeito a quando ambas as entradas J e K são ativas ao mesmo tempo. No FF SR esta situação gera saída ambígua, já no FF JK ela tem o mesmo efeito da entrada T do FF T, ou seja, após a atuação conjunta das entradas J e K, a saída Q terá sido complementada no FF JK.

A tabela verdade do FF JK é então assim definida, sendo QA a mesma saída Q antes da atuação das

entradas J e K:

Entrada J Entrada k Saída QA Saída Q

0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 1 1 0 1 0 0 1 1 0 1 1

Ent J

Ent K

Saída QA

anterior atuação T Saída Q posterior atuação T Ent S Ent R

0 0 0 0 1 1

0 0 1 1 1 1

0 1 0 0 1 1

0 1 1 0 1 0

1 1 0 1 0 1

1 1 1 0 1 0

1 0 0 1 0 1

1 0 1 1 1 1

Retirando-se as expressões para as entradas do FF SR, pelo Mapa de karnaugh tem-se:

Mapa para a entrada S

JK

QA 00 01 11 10

0 0 0 S =JQ

A

1

Mapa para entrada R

JK

QA 00 01 11 10

0 R=KQA

1 0 0

Implementando-se o circuito do Flip-Flop tipo JK tem-se:

_ S _ R Q _ Q J k

FLIP-FLOP JK COM CLOCK

De forma análoga ao FF RS o FF JK também pode ser disparado por borda de pulso de clock. Uma versão simplificada do circuito interno de um FF JK disparado por transição de pulso de clock é mostrada na figura abaixo.

A simbologia e tabela verdade para o FF JK disparado por transição de subida de pulso de clock está mostrada na figura (a) que se segue. A carta de tempo para esse FF está representado na figura (b).

5) FLIP-FLOP TIPO D

Diferentemente dos FF RS e JK anteriormente estudados, o Flip-Flop tipo D tem apenas uma entrada de controle síncrona, entrada D, que representa a palavra data (dados). A operação do FF D consiste em que a saída Q irá para o mesmo estado lógico presente na entrada D quando ocorrer uma transição do pulso de clock. Em outras palavras, o nível lógico presente na entrada D será armazenado no FF no instante em que ocorrer a borda do clock. Eles podem ser chaveados por borda positiva ou por borda negativa do pulso de clock.

A implementação da função D é obtida utilizando-se um FF SR, conforme demonstrado na figura seguinte.

A simbologia e tabela verdade para o FF D disparado por transição de subida de pulso de clock está mostrada na figura (a) que se segue. A carta de tempo para esse FF está representado na figura (b).

LATCH D (LATCH TRANSPARENTE)

O FF tipo D visto, possui um circuito detector de borda, que se encontra no FF JK utilizado para sua implementação, o que garante que a saída responda à entrada D somente quando ocorre uma transição ativa do pulso de clock. Se esse detector de borda não for usado, o circuito resultante é denominado Latch D.

O circuito contém um FF SR (Set-Reset) ou SC (Set-Clear) e um direcionador de pulso formados por portas NAND, porém não possui o circuito detector de borda. A entrada comum das portas que implementam o circuito direcionador é denominada entrada de habilitação (enable, abreviado por EN), em vez de denominação de clock, uma vez que seu efeito na saída não está restritos às transições.

Seu funcionamento se resume no fato de que enquanto a entrada de habilitação EN é 0, a saída Q do Latch D não é alterada, pois as saídas das portas NAND 1 e 2 ficam em estado 1, e nesse estado o Latch NAND não tem seu estado alterado. Quando a entrada de habilitação EN está em estado 1, as portas NAND 1 e 2 permitem que o nível presente na entrada D seja invertida e alimente apropriadamente as entradas do Latch NAND, ou seja, se D for 1, SET recebe 0 e CLEARrecebe 1, levando a saída Q para o nível 1. Caso D seja 0, SET recebe 1 e CLEARrecebe 0, levando a saída Q para o nível 0. Em outras palavras, enquanto EN for 1, a saída Q será igual a entrada D, e nesse momento, pode-se dizer que o latch D é transparente. A carta de tempo que demonstra a operação do Latch D está representada na figura seguinte.

ENTRADAS SÍNCRONAS E ASSÍNCRONAS

entrada clock (CLK). A maioria dos FFs com clock também tem uma ou mais entradas assíncronas, que operam independentemente das entradas síncronas e da entrada de clock. Essas entradas assíncronas podem ser utilizadas para colocar o FF no estado 1 ou 0 em qualquer instante, independentemente das condições das outras entradas.

A figura seguinte mostra a simbologia e tabela verdade relacionando a saída e as entradas assíncronas de um FF JK, por exemplo.

6) TEMPORIZAÇÃO DE FLIP-FLOPS

Os fabricantes de CIs de Flip-Flops especificam vários parâmetros de temporização importantes e características que tem que ser consideradas para utilização de FFs. Como exemplo, a tabela a seguir , exibe os mais importantes parâmetros de temporização de alguns CIs de FFs comerciais das famílias TTL e CMOS, listados abaixo.

• 7474 – Duplo FF D disparado por borda (TTL padrão)

• 74LS112- Duplo FF JK disparado por borda ( TTL Schottky de baixa potência)

• 74C74 – Duplo FF D disparado por borda (CMOS de porta metálica)

• 74HC112 – Duplo FF JK disparado por borda (CMOS de alta velocidade)

Tempo-rização

Descrição CI Família TTL

(em ns)

CI Família CMOS (em ns)

7474 74LS112 74C74 74HC112

t Tempo de setup 20 20 60 25

tH Tempo de hold 5 0 0 0

tPHL Propagação de CLK para Q 40 24 200 31

tPLH Propagação de CLK para Q 25 16 200 31

tPHL Propagação de CLR para Q 40 24 225 41

tPLH Propagação de PREpara Q 25 16 225 41

tw(L) Tempo de CLK em nível baixo 37 15 100 25

tw(H) Tempo de CLK em nível alto 30 20 100 25

tw(L) Tempo de PREou CLRem nível baixo 30 15 60 25

fMAX Em MHz 15 30 5 20

Em se tratando de problemas pontenciais decorrentes de temporização, dois parâmetros de temporização de FFs são especialmente importantes: o tempo de setup (preparação) e o tempo de hold (manutenção).

O tempo de setup, tS, de um FF é o intervalo de tempo que precede imediatamente a transição ativa do

sinal de clock durante o qual as entradas de controle síncronas tem que ser mantidas nos níveis adequados.

O tempo de hold, tH, de um FF é o intervalo de tempo que segue imediatamente após a transição ativa

7) FLIP-FLOP MESTRE-ESCRAVO

Em muitos circuitos digitais, a saída de um FF é conectada, diretamente ou por meio de portas lógicas, à entrada de outro FF, e ambos são disparados pelo mesmo pulso de clock. Isso representa um problema potencial de temporização.

A próxima figura apresenta um exemplo de um circuito com essa situação. O problema potencial de temporização é que Q1 muda de estado na borda negativa do pulso de clock, então, a entrada J2 de Q2

estará mudando de estado quando recebe a mesma borda de descida do pulso de clock. Isto pode conduzir a uma resposta imprevisível de Q2.

Na figura anterior, considerando-se Q1=1 e Q2=0, assim o FF Q1 possui J1=K1, e Q2 possui J2=Q1=1 e

K2=0 antes da borda de descida do pulso de clock. Quando ocorre a borda de descida de clock, Q1

comuta para o estado 0, mas isso só ocorre depois de decorrido o tempo de propagação tPHL. A mesma

borda negativa dispara Q2 de modo confiável para o estado 1 desde que tPHL seja maior que o tempo de

Todos FFs recentes disparados por borda tem um tempo de hold de 5 ns ou menos. A maioria possui tH

= 0, o que significa que eles não necessitam de tempo de hold. Para estes FFs não há o problema potencial de temporização.

Antes do desenvolvimento dos FFs disparados por borda que requerem um tempo de hold pequeno ou nulo, os problemas de temporização acima relatados eram frequentemente tratados usando uma classe de FFs denominada FF Mestre-Escravo.

Um FF Mestre-Escravo é constituído de dois FFs, um Mestre e um Escravo. Na borda de subida do sinal de clock, os níveis presentes nas entradas síncronas (D, J, K) são usados para determinar a saída interna do FF Mestre. A carta seguinte demonstra a temporização dos FFs internos, Mestre e Escravo. Quando o sinal de clock vai para nível baixo, o estado do FF Mestre é transferido para o FF Escravo, cujas saídas são as saídas Q e Q do FF Mestre_Escravo. Assim as saídas Q e Q do FF Mestre-Escravo funcionam de maneira muito semelhante com os FFs disparados por borda negativa, exceto que as entradas de controle tem que ser mantidas estáveis quando o pulso de clock estiver em nível alto. Este problema foi resolvido com uma versão do FF Mestre-Escravo melhorada denominada Mestre-Escravo com travamento de dados (data lockout). Este tipo de Flip-Flop tornou-se obsoleto.

Ent. S

Ent. R

CLK

QM

QE=QFF

CAPÍTULO 3

CIRCUITOS CONTADORES

Os circuitos contadores são uma finalidade especial dos circuitos digitais, compostos de FFs, que têm a função de contar o número de eventos de um determinado sistema. Um contador de N, que é capaz de contar até um especificado número N de eventos, irá necessitar de K Flip-Flops, onde 2K≥N.

REVISÃO DE CÓDIGOS BINÁRIO-DECIMAL

Em computadores e outros sistemas lógicos binários, a informação e os dados são tratados na forma de representação binária. Entretanto, para o homem, o sistema de representação numérica decimal é a forma mais conveniente. Assim, a codificação e decodificação de números decimais em binários se torna necessária para conciliar as quantidades tratadas pelos circuitos digitais, na forma binária, e a representação de melhor entendimento para o homem, ou seja, a decimal.

A seguir estão representados alguns dos mais conhecidos códigos de representação de Decimal Codificado em Binário (BCD) de 4 bits. Nestes códigos são necessários 4 bits, ou dígitos binários, para representação de um dígito decimal.

CÓDIGOS BCD NÚMERO

DECIMAL 8 4 2 1 2 4 2 1 7 4 2 1 5 2 1 1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 2 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 3 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 4 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 1 5 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 0 6 0 1 1 0 0 1 1 0 0 1 1 0 1 0 0 1 7 0 1 1 1 0 1 1 1 1 0 0 0 1 0 1 1 8 1 0 0 0 1 1 1 0 1 0 0 1 1 1 0 1 9 1 0 0 1 1 1 1 1 1 0 1 0 1 1 1 1

Exemplos de representação de números decimais em BCD:

73(10)= 0111.0011(BCD 8421)

92(10)= 1111.0010(BCD 2421)

395(10)= 0011.1010.0101(BCD7421)

1) CONTADORES ASSÍNCRONOS

Esse contador recebe a designação de Contador Assíncrono, porque os FFs de seus diversos estágio não mudam de estado em sincronismo com o clock de entrada, apenas o primeiro estágio está sincronizado com o clock de entrada.

Nos sistemas assíncronos de contagem existe um determinado tempo para que todas as mudanças nos diversos FFs que compõem o sistema ocorram. O atraso ocorrido em cada FF é na ordem de 5 a 20 ns. O tempo gasto para a realização de uma contagem de evento depende do número total de FFs envolvidos.

Esse circuito recebe outras designações alternativas. Por exemplo, como a saída de cada FF aciona a entrada de clock do FF seguinte, dá-se o nome de Contador Série, que se refere à forma de propagação do clock pelos diversos FFs de seus estágios. Ele também é frequentemente denominado de

Contador Ondulante (Ripple Counter), devido a maneira dos FFs responderem um após o outro de modo análogo à propagação de uma onda. Finalmente, em função das contagens apresentadas nas saídas dos seus FFs apresentarem a mesma seqüência do sistema de numeração binário, ele também pode ser denominado de Contador Binário Puro.

CONTADORES DIRETOS E INVERSOS

Contadores diretos ou crescentes, ou simplesmente UP contam os eventos em ordem direta, desde um número menos significativo para um número mais significativo. Os contadores inversos ou decrescentes, ou simplesmente DOWN, contam os eventos em ordem inversa, ou seja, desde um número mais significativo para um número menos significativo.

CONTAGEM DIRETA CONTAGEM

INVERSA Saídas Contador Saídas Contador Valor Decimal

D C B A

Valor Decimal

D C B A

0 0 0 0 0 15 1 1 1 1

1 0 0 0 1 14 1 1 1 0

2 0 0 1 0 13 1 1 0 1

3 0 0 1 1 12 1 1 0 0

4 0 1 0 0 11 1 0 1 1

5 0 1 0 1 10 1 0 1 0

6 0 1 1 0 9 1 0 0 1

7 0 1 1 1 8 1 0 0 0

8 1 0 0 0 7 0 1 1 1

9 1 0 0 1 6 0 1 1 0

10 1 0 1 0 5 0 1 0 1

11 1 0 1 1 4 0 1 0 0

12 1 1 0 0 3 0 0 1 1

13 1 1 0 1 2 0 0 1 0

14 1 1 1 0 1 0 0 0 1

Os contadores UP-DOWN são aqueles que podem contar diretamente ou inversamente, bastando para isso que sejam assim comandados.

As tabelas anteriores expõem as saídas dos quatro estágios de um contador em binário puro e os sentidos das contagens. Nas tabelas anteriores a saída D representa o dígito binário (bit) mais significativo e a saída A representa o bit menos significativo.

CONTADOR ASSÍNCRONO DIRETO (CONTADOR UP)

Da tabela de contagem direta, pode-se observar que o dígito imediatamente mais significativo muda de estado toda vez que a saída do estágio anteriormente menos significativa muda de 1 para 0. Quanto ao dígito menos significativo do conjunto, saída A, ele muda de estada a cada pulso de entrada. Essas condições são satisfeitas pelo FF tipo T, chaveado na descida do pulso de clock.

O circuito do contador assíncrono de 0 a 15, contagem direta, utilizando FFs JK, com as entradas J=1 e K=1 para implementar a função FF tipo T, e a sua respectiva carta de tempo se encontram mostrados na figura seguinte.

CONTADOR ASSÍNCRONO INVERSO (CONTADOR DOWN)

de 0 para 1. Quanto ao dígito menos significativo do conjunto, saída A, ele muda de estada a cada pulso de entrada.

Essas condições são satisfeitas pelo FF tipo T, chaveado na subida do pulso de clock, excetuando-de o FF A que ainda tem que ser comutado na transição negativa do pulso de clock de entrada. Assim, em contador inverso cada FF, exceto o primeiro tem de comutar quando o FF decrescente passa do nível 0 para o nível 1.

Para implementar-se esse contador faz-se necessário que ao invés de se utilizar a saída Q para alimentar a entrada clock do FF do próximo estágio mais significativo, utiliza-se então a saída negada ( Q ), o que vai satisfazer a necessidade de comutação nas transições de 0 para 1.

O circuito do contador assíncrono de 7 a 0, contagem inversa, utilizando FFs JK, com as entradas J=1 e K=1 para implementar a função FF tipo T, e a sua respectiva carta de tempo se encontram mostrados na figura seguinte.

MÓDULO DE UM CONTADOR

O contador síncrono direto visto anteriormente tem 16 estados de saída distintos (de 0000 a 1111). Ele é um contador série de módulo 16. O módulo é sempre igual ao número de estados que o contador percorre em cada ciclo completo de contagem antes de retornar ao estado original.

O contador básico pode ser utilizado para gerar um módulo menor que 2N. Isto ocorre fazendo-se que contador não exiba estados de saída, contagens, que normalmente fazem parte da seqüência de contagem. O circuito e a sua correspondente carta de tempo mostrados na figura a seguir é de um contador de 3 FFs, portanto seu módulo ≤ 23≤8.

Para reduzir seu módulo está demonstrada a utilização de uma porta lógica para decodificação das saídas e utilização das entradas assíncronas CLRpara alteração da seqüência de contagem. A porta NAND é utilizada para forçar a mostragem de contagem 0, através da ativação da entrada CLRtoda vez que o contador apresentar a contagem 6, ou seja B e C=1. Assim o contador mostrará somente as contagens 000,001,010,011,100,101, e retornará a 000, repetindo o ciclo. Como o contador apresenta somente 6 estados diferentes de contagem, ele é um contador módulo 6.

Deve ser observado que a forma de onda na saída B contém um spike ou glitch causado pela ocorrência momentânea do estado 110 antes de ir para 000.

CIRCUITOS DIVISORES POR N

assim a freqüência de saída será N vezes menor que a freqüência de entrada do evento de entrada. Tal ocorrência pode ser verificada na forma de onda da saída C do contador módulo 6 visto acima, ou seja, a freqüência do sinal de saída em C é a freqüência de clock dividida por 6.

A ilustração da divisão de freqüência se encontra na figura que se segue. Considerando que a freqüência de clock da carta de saída do contado assíncrono de 16 eventos visto anteriormente, abaixo representada seja 16 KHz, a saída do FF A é uma onda quadrada de 8 KHz, ou seja, a freqüência do clock dividida por 2; a saída do FF B é uma onda quadrada de 4 KHz, ou seja, a freqüência do clock dividida por 4; a saída do FF C é uma onda quadrada de 2 KHz, ou seja, a freqüência do clock dividida por 8; a saída do FF D é uma onda quadrada de 1 KHz, ou seja, a freqüência do clock dividida por 16.

Como exemplo da utilização de contadores na divisão de frequência, o contador exibido na próxima figura é um contado de módulo 10, ou contador decádico, ou contador BCD. Os contadores decádicos tem ampla utilização na divisão de frequência do eventos a serem contados, ou seja, pulsos de clock, por 10. Os pulsos de saída, com a frequência dividida por 10, são obtidos na saída do FF D. No exemplo a frequência de clock de 1 MHz, aparece no sinal da saída D com 100 KHz.

DECODIFICAÇÃO DE CONTAGENS ESPECÍFICAS

Os sistemas digitais às vezes são requeridos para gerar um pulso quando um contador alcança um contagem previamente determinada. Nesse caso é necessário um decodificador para realizar essa função. O decodificador é obtido com portas lógicas AND ou NAND, cujas entradas são as saídas Q e

O circuito visto anteriormente, contador decádico ou BCD, mostra um contador assíncrono de módulo 16 com um decodificador para detecção de contagem 10. Em outras palavras a saída da porta NAND deverá apresentar um nível lógico 0 a cada vez que o contador apresentar a contagem 10 nas saídas dos seus FFs. No caso deste circuito o resultado da detecção da contagem 10 é utilizada para retorna-lo à contagem 0 toda vez que a contagem 10 é alcançada.

CIRCUITOS INTEGRADOS DE CONTADORES ASSÍNCRONOS

Existem vários CIs contadores assíncronos das famílias TTL e CMOS. Como exemplo será ilustrado o CI TTL 74LS293. O diagrama lógico deste CI é mostrado na figura (a) seguinte. A figura (b) exibe o símbolo lógico e respectiva pinagem.

O CI 74LS293 possui quatro FFs JK com as saídas Q0(LSB), Q1, Q2 e Q3(MSB). As entradas de clock,

ativas na transição negativa, para o FF1 e o FF2, são respectivamente, os pinos CP0 (clock pulse) e

CP1. Os pinos MR1 (master reset) e MR2 alimentam as entradas CLEAR (CD) de cada FF, através de

uma porta lógica NAND.

ASSOCIAÇÃO DE CIs DE CONTADORES ASSÍNCRONOS

Como exemplo de decodificação de contagens específicas e da possibilidade de construir-se contadores de módulos maiores a partir da disponibilidade de contadores de módulos menores, está exposto na figura seguinte, um contador de módulo 60, ou divisor por 60, constituído da associação de um contador de módulo 10 e um contador de módulo 6.

Neste circuito, contador de 60 eventos, cabe ressaltar que ambos os contadores de módulo 10 e módulo 6, foram construídos com CI 74LS293, onde foi utilizada a decodificação das contagens 10 e 6, respectivamente, e a saída mais significativa do primeiro contador, ou seja saída dividida por 10, ou com sinalização de contagem 10 alimenta a entrada de clock do segundo contador, de módulo 6 ou divisor por 6.

2) CONTADORES SÍNCRONOS OU PARALELOS

Como visto nos contadores assíncronos o tempo gasto para contar um evento é dependente do número total de estágios componentes do contador. Nos contadores síncronos, ou paralelos, as entradas de clock são alimentadas em paralelo pelo mesmo clock, e as mudanças dos estado dos FFs ocorrem simultaneamente.

Como o sinal de clock é aplicado simultaneamente em todos os FFs, é necessátrio que as entradas síncronas de cada FF estejam preparadas para que cada FF mude no instante apropriado. Esse efeito é obtido utilizando-se a decodificação dos próprios sinais de saída dos FFs para alimentação das entradas sícronas de cada estágio.

As próximas figuras (a) e (b) exibem respectivamente o circuito de um contador síncrono módulo 16 e a tabela contendo cada um das contagens que ele exibe, entre 0 e 15.

ocorrência de transição ativa do pulso de clock. O estágio menos significativo, FF A, muda de estado a cada pulso de clock.

TEMPORIZAÇÃO DE CIRCUITOS CONTADORES

No contador síncrono todos os FFs mudam de estado simultaneamente. Assim, diferentemente dos contadores assíncronos, os atrasos de propagação dos FFs não são somados para se obter o atraso total. Em vez disso, o tempo total de resposta de um contado síncrono, como o anteriormente mostrado, é o tempo de resposta de um FF para comutar mais o tempo para os novos níveis lógicos se propagarem por uma única porta lógica AND. Então no contador síncrono:

atraso total= tempo de propagação do FF + tempo de propagação da porta AND

utilizados FFs com tempo de propagação de 50 ns e portas lógicas (somente no contador síncrono) com tempo de propagação 20 ns, a máxima frequência de clock de entrada a ser contada é :

Para o contador síncrono

fmax=1/Tclock, onde Tclock=50+20=70 ns ; fmax=1/70 ns = 14,3 MHz

Para o contador assíncrono (4 FFs):

fmax=1/Tclock, onde Tclock=4x50=200 ns ; fmax=1/200 ns = 5,0 MHz

CONTADORES COM CARGA PARALELA

Muitos contadores síncronos (paralelos) disponíveis em CIs podem ser carregáveis (presettable), ou seja, podem ser inicializados com qualquer valor inicial antes do início da contagem. Essa operação de inicialização também é denominada de carga paralela. A figura seguinte mostra o circuito lógico de um contador up de três bits com carga paralela.

A maioria dos contadores conta os eventos numa seqüência binária normal, embora suas seqüências possam ser alteradas utilizando métodos já vistos. Existem situações, entretanto, que um contador deve seguir uma seqüência diferente da seqüência de numeração binária, como por exemplo, quando utiliza códigos de 4 bits diferentes do BCD 8421.

Para ilustrar uma situação dessas, será abordado o projeto de um contador síncrono decádico módulo 10, utilizando FFs JK cuja contagem dos eventos deve ser mostrado utilizando-se o código BCD 2421.

O contador desejado é de módulo 10 (N), portanto o número (K) de FFs a serem utilizados deve atender a equação 2K≥N. Então K=4, ou seja, o contador precisa de 4 FFs.

Passo 1 – Tabela de contagem para o código BCD 2421

Contagem Decimal

D C B A 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 1 1 0 9 1 1 1 1 10-15 - - - -

Nas tabelas e mapas utilizados no projeto, para qualquer combinação de entradas ou resultado na saída que não interesse ou que nunca deva ocorrer será utilizada a notação “ - ” em substituição aos níveis lógico 0 e 1.

Passo 2– Mapa de karnaugh para a contagem desejada

DC

BA 00 01 11 10 00 0 4 - - 01 1 5 - - 11 3 7 9 - 10 2 6 8 -

Passo 3 – Mapa de mudanças para o tipo de FF utilizado

Níveis lógicos Mudança na saída Q

J K

0->1 (Mudança de 0 para 1) 1 - 1->0 (Mudança de 1 para 0) - 1

0->0 (0 mantido) 0 -

1->1 (1 mantido) - 0

Passo 4 – Mapa de mudanças para cada FF do contador

Observa-se que pela seqüência de contagens na tabela de contagem, que o FF C após a contagem 3 deverá estar preparado para a próxima contagem, 4, onde irá de 0->1 e que na contagem 4 deverá estar preparado para a próxima contagem, 0, onde irá de 1->0. Essas mudanças devem ser descritas no Mapa de Mudanças do FF C. Isso deverá ser feito para todos os FFs do contador.

Mapa Contagem Mapa Mudanças FF D

DC DC

BA 00 01 11 10 Æ BA 00 01 11 10

00 0 4 - - 00 0->0 0->0 - -

01 1 5 - - 01 0->0 0->0 - -

11 3 7 9 - 11 0->0 0->1 1->0 -

10 2 6 8 - 10 0->0 0->0 1->1 -

Mapa Contagem Mapa Mudanças FF C

DC DC

BA 00 01 11 10 Æ BA 00 01 11 10

00 0 4 - - 00 0->0 1->1 - -

01 1 5 - - 01 0->0 1->1 - -

11 3 7 9 - 11 0->1 1->1 1->0 -

10 2 6 8 - 10 0->0 1->1 1->1 -

Mapa Contagem Mapa Mudanças FF B

DC DC

BA 00 01 11 10 Æ BA 00 01 11 10

00 0 4 - - 00 0->0 0->0 - -

01 1 5 - - 01 0->1 0->1 - -

11 3 7 9 - 11 1->0 1->1 1->0 -

10 2 6 8 - 10 1->1 1->1 1->1 -

Mapa Contagem Mapa Mudanças FF A

DC DC

BA 00 01 11 10 Æ BA 00 01 11 10

00 0 4 - - 00 0->1 0->1 - -

01 1 5 - - 01 1->0 1->0 - -

11 3 7 9 - 11 1->0 1->0 1->0 -

10 2 6 8 - 10 0->1 0->1 0->1 -

Os mapas de mudança de cada FF devem ser associados às condições de J e K para mudança de saída do FF JK.

Mapa Mudanças FF D Mapa JDKD

DC CB

BA 00 01 11 10 Æ BA 00 01 11 10

00 0->0 0->0 - - 00 0 - 0 - - - - -

01 0->0 0->0 - - 01 0 - 0 - - - - -

11 0->0 0->1 1->0 - 11 0 - 1 - - 1 - -

10 0->0 0->0 1->1 - 10 0 - 0 - - 0 - -

Mapa Mudanças FF C Mapa JCKC

DC CB

BA 00 01 11 10 Æ BA 00 01 11 10

00 0->0 1->1 - - 00 0 - - 0 - - - -

01 0->0 1->1 - - 01 0 - - 0 - - - -

11 0->1 1->1 1->0 - 11 1 - - 0 - 1 - -

10 0->0 1->1 1->1 - 10 0 - - 0 - 0 - -

Mapa Mudanças FF B Mapa JBKB

DC CB

BA 00 01 11 10 Æ BA 00 01 11 10

00 0->0 0->0 - - 00 0 - - 0 - - - -

01 0->1 0->1 - - 01 1 - - 1 - - - -

11 1->0 1->1 1->0 - 11 - 1 - 0 - 1 - -

10 1->1 1->1 1->1 - 10 - 0 - 0 - 0 - -

Mapa Mudanças FF A Mapa JAKA

DC CB

BA 00 01 11 10 Æ BA 00 01 11 10

00 0->1 0->1 - - 00 1 - 1 - - - - -

01 1->0 1->0 - - 01 - 1 - 1 - - - -

11 1->0 1->0 1->0 - 11 - 1 - 1 - 1 - -

10 0->1 0->1 0->1 - 10 1 - 1- 1 - - -

Passo 6 – Mapa de J e K para cada FF do contador

Mapa JD Mapa KD

DC DC

BA 00 01 11 10 BA 00 01 11 10

00 0 0 - - 00 - - - -

01 0 0 - - 01 - - - -

11 0 1 - - 11 - - 1 -

10 0 0 - - 10 - - 0 -

JD=CBA KD=A

Mapa JC Mapa KC

DC DC

BA 00 01 11 10 BA 00 01 11 10

00 0 - - - 00 - 0 - -

01 0 - - - 01 - 0 - -

11 1 - - - 11 - 0 1 -

10 0 - - - 10 - 0 0 -

JC=BA KC=DA

Mapa JB Mapa KB

DC DC

BA 00 01 11 10 BA 00 01 11 10

00 0 0 - - 00 - - - -

01 1 1 - - 01 - - - -

11 - - - - 11 1 0 1 -

10 - - - - 10 - 0 0 -

JB=A KB=DA+CA=A(D+C)

Mapa JA Mapa KA

DC DC

BA 00 01 11 10 BA 00 01 11 10

00 1 1 - - 00 - - - -

01 - - - - 01 1 1 - -

11 - - - - 11 1 1 1 -

10 1 1 1 - 10 - - - -

JA=1 KA= 1

As expressões lógicas para as entradas síncronas J e K de cada FF, estão reunidas a seguir: JD=CBA KD=A

JC=BA KC=DA

JB=A KB=DA+CA=A(D+C)

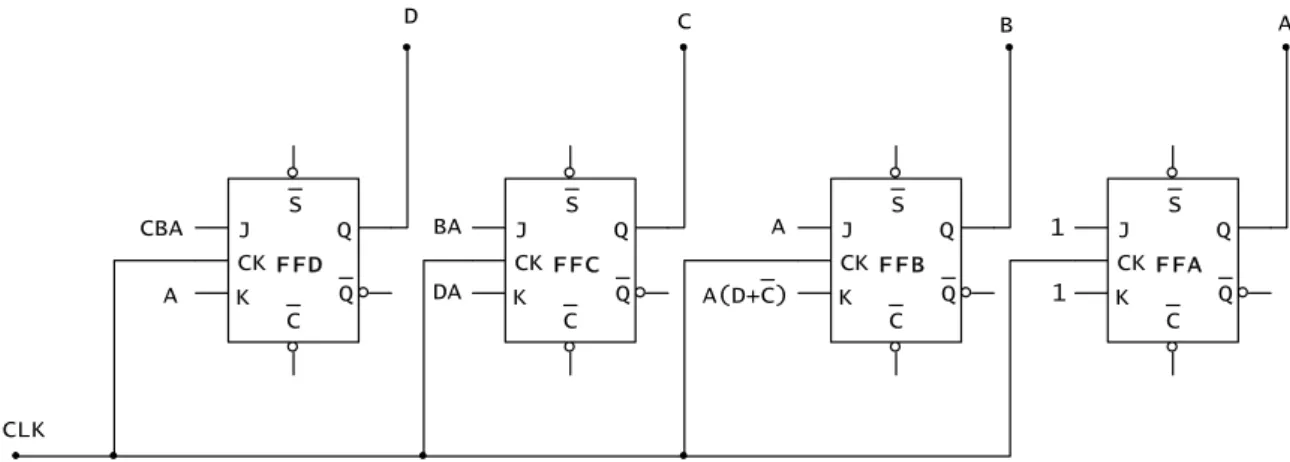

O circuito do contador síncrono decádico em código BCD 2421 se encontra implementado na figura a seguir. No circuito não estão expostas as portas lógicas que codificam as impressões assinaladas nas entradas J e K dos FFs a partir das saídas Q dos diversos estágios. As entradas assíncronas não são utilizadas e devem ser conectadas ao nível lógico 1.

J K CK Q _ Q _ S _ C FFD J K CK Q _ Q _ S _ C FFC J K CK Q _ Q _ S _ C FFB J K CK Q _ Q _ S _ C FFA 1 1

D C B A

CLK CBA A BA DA A _ A(D+C)

PROJETO DE CONTADOR SÍNCRONO BIDIRECIONAL (UP-DOWN)

Nesta parte será demonstrado um projeto de contador síncrono bidirecional. O projeto será para um contador com saídas de contagem em binário puro de módulo 4 utilizando FFs JK.

Tabela e Mapa de Karnaugh para o contador

Tabela Mapa da Contagem

Decimal B A BA 00 01 11 10

0 0 0 0 1 3 2

1 0 1

2 1 0

3 1 1

O projeto de contador up-down torna necessária a realização em duas etapas, a primeira para o contador up e a segunda para o contador down.

A- PROJETO DO CONTADOR SÍNCRONO UP

Mapas de Mudanças

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

Mapas JK

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

0 - 1 - - 1 - 0 1 - - 1 - 1 1 -

Mapas J

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

0 1 - - 1 - - 1

JB=A JA=1

Mapas K

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

- - 1 0 - 1 1 -

KB=A KA=1

B- PROJETO DO CONTADOR SÍNCRONO DOWN

Mapas de Mudanças

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

0->1 0->0 1->1 1->0 0->1 1->0 1->0 0->1

Mapas JK

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

1 - 0 - - 0 - 1 1 - - 1 - 1 1 -

Mapas J

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

1 0 - - 1 - - 1

Mapas K

FF B FF A

BA 00 01 11 10 BA 00 01 11 10

- - 0 1 - 1 1 -

KB=A KA=1

C- PROJETO DO CONTADOR SÍNCRONO UP-DOWN

As entradas lógicas para o contador up-down são obtidas combinando-se logicamente as entradas lógicas do contador up com as entradas lógicas do contador down. Para permitir o chaveamento entre os dois modos de operação será utilizada uma linha lógica F, que será 1 para a contagem up e 0 para a contagem down. A tabela a seguir expõe a combinação lógica desejada.

Contador Up OU Contador Down Contador Up-Down

JB= F.A + JB= F.A = F.A+F.A

KB= F.A + KB= F.A = F.A+F.A

JA= F.1 + JA= F.1 = 1

KA= F.1 + KA= F.1 = 1

Levando-se em conta que quando selecionada a contagem up (F=1), a contagem down (F=0) estará desabilitada pois a lógica comandada por F não permitirá que as entradas do FF B receba os níveis projetados para o contador down; ao contrário somente será permitido o acesso ao FF B dos níveis projetados para o contador up. A situação inversa também é verdadeira.

Como visto na tabela anterior, as entradas JB e KB do contador Up-Down possuem a mesma expressão

lógica F.A+F.A, e as entradas JA e KA possuem níveis lógicos 1. O circuito implementado para o

contador Up-Down está exposto a seguir.

J K CK B _ B _ S _ C

F FD J

K CK A _ A _ S _ C F FD CLOCK F _ F

F=1 - CONT UP F=0 - CONT DOWN

1

1

CONTADOR SÍNCRONO DE MÓDULO 8 UP/DOWN

clock, positiva ou negativa, provenientes das saídas dos estágios anteriores, se alimenta as entradas síncronas dos estágios posteriores.

No contador Up, o FF imediatamente mais significativo muda de estado toda vez que a saída do estágio anteriormente menos significativa muda de 1 para 0, ou seja, sofre uma transição positiva. Nesse contador, para alimentação das entradas síncronas do estágio sucessor, utiliza-se as transições ocorridas nas saídas Q dos estágios antecessores.

No contador Down, o FF imediatamente mais significativo muda de estado toda vez que a saída do estágio anteriormente menos significativa muda de 0 para 1, ou seja, sofre uma transição negativa. Nesse contador, para alimentação das entradas síncronas do estágio sucessor, utiliza-se as transições ocorridas nas saídas Q dos estágios antecessores.

A figura a seguir exibe um contador síncrono de módulo 8 Up/Down. A lógica adicional OU no circuito permite o chaveamento pelas saídas Q, no modo Up, ou Q , no modo Down. O sinal de seleção

Up/Down chaveia a opção desejada.

CONTAGENS IRREGULARES E TRUNCADAS

No projeto de contadores síncronos com FFs JK verificamos ser possível construir circuitos contadores para executar a contagem em qualquer seqüência de códigos binários estipulado previamente. Se comparado o código BCD 8421 com uma contagem binária em quatro bits, o código BCD 8421 é uma contagem truncada. Os circuitos digitais às vezes necessitam de contagens irregulares, fora da sequência natural de grandeza das quantidades decimais, ou truncadas, ou seja, contagens encerradas em determinada grandeza decimal retornando, após essa grandeza à contagem desde o início.

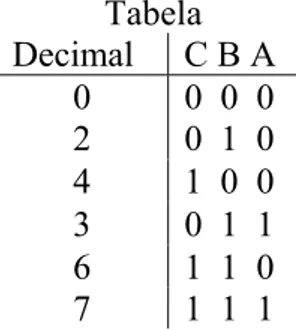

Para exemplificação dessa possibilidade em projetos de contadores pelo método dos Mapas de Karnaugh, será ilustrado o projeto de um contador para uma saída de contagem irregular e truncada.

PROJETO DE CONTADOR SÍNCRONO UTILIZANDO FF TIPO D

Para o FF tipo D, deve-se levar em conta que quando o contador estiver exibindo a contagem presente, as entradas D dos FFs devem estar com os estados a serem apresentados pela próxima contagem a ser exibida, pois quando houver a ocorrência do próximo evento contado, ou seja, o próximo pulso de clock, os FFs mudarão de estado apresentando em suas saídas os estados atuais de suas respectivas entradas D.

Passo 1 – Tabela e Mapa de Karnaugh para contagem irregular e truncada

Tabela Mapa de Karnaug

Decimal C B A

0 0 0 0 CB

2 0 1 0 A 00 01 11 10

4 1 0 0 0 0 2 6 4

3 0 1 1 1 - 3 7 -

6 1 1 0 7 1 1 1

Passo 2 – Tabela de estados presentes e próximos

Contagem Presente

C B A Contagem Próxima

DC DB DA

Passo 3 – Mapas D dos FFs e expressões de entradas

Mapas para entradas D das contagens futuras

Mapa DC Mapa DB Mapa DA

CB CB CB

A 00 01 11 10 A 00 01 11 10 A 00 01 11 10

0 0 1 1 0 0 1 0 1 1 0 0 0 1 1 1 - 1 0 - 1 - 1 0 - 1 - 0 0 -

DC=CB+BA DB=B+CA+CA DA=CA

O circuito do contador síncrono para a contagem determinada se encontra implementado na figura a seguir. No circuito não estão expostas as portas lógicas que codificam as impressões assinaladas nas entradas D dos FFs a partir das saídas Q dos diversos estágios. As entradas assíncronas não são utilizadas e devem ser conectadas ao nível lógico 1.

D CLK FF C S R C _ C D CLK FF B S R B _ B D CLK FF A S R A _ A 0

0 0 0

0 0 _ _ CB+BA _ _ _ B+CA+CA _ CA

CIRCUITOS INTEGRADOS DE CONTADORES SÍNCRONOS

Exemplificando a funcionalidade do CI 74 LS193 como contador crescente estão as figuras acima (a) representando a interconexão do CI ao circuito, onde as entradas de dados paralelos estão permanentemente conectadas aos níveis 1011 e (b) a carta de tempo do circuito, considerando-se que o contador está inicialmente em 0000.

No próximo exemplo, o CI 74LS193 está sendo utilizado como contador decrescente, sendo que a figura (a) mostra sua interligação ao circuito, onde as entradas de dados paralelos estão permanentemente conectadas aos níveis 0111 e (b) a carta de tempo do circuito, considerando-se que o contador está inicialmente em 0000.

CONTADOR DE MÓDULO VARIÁVEL UTILIZANDO CI 74LS193

Os contadores que permitem carga paralela podem ser conectados para se obter módulos diferentes sem a necessidade de utilização de portas lógicas adicionais para decodificação.

As lógicas para geração dos pulsos TCU e TCD no CI 74LS193 são as mostradas nas figuras (a) e (b)

O circuito da figura (a) abaixo expõe a implementação de um contador de módulo 5 pelo CI 74LS193, que é de módulo 16. O contador em questão é decrescente, e apresenta em sua saída as contagens de 5 a 0. A carta de tempo do circuito exposta na figura (b) demonstra que o contador é decrementado nas transições positivas de CPD nos instantes de t1 até t5. Em t5 o contador está no estado 0000. Quando CPD

vai para 0 em t6 ele força TCD a ir para 0. Isto imediatamente ativa a entrada PLque coloca o contador

de volta no estado 0101. Deve ser observado que o pequeno intervalo de tempo de permanência em 0 de

TCD se deve ao fato de que a saída do contador ao apresentar brevemente este estado 0000 é

ASSOCIAÇÃO DE CIs CONTADORES SÍNCRONOS

As saídas TCU e TCD são utilizadas quando há necessidade de utilização de diversos CIs para

construção de contadores com módulo maior. Como exemplo, a figura seguinte mostra dois CIs conectados para formar um contador crescente/decrescente de dois estágio para aumentar efetivamente o intervalo de contagem de 0-15 de cada CI individual para 0-255 (4 FFs em cada estágio). O estágio à esquerda é o estágio de mais baixa ordem e é disparado pela entrada de clock crescente ou pela entrada de clock decrescente. As saídas deste estágio, TCU e TCD, são conectadas às entradas de clock do