UNIVERSIDADEFEDERALDO RIO GRANDE DO NORTE P

ROGRAMA DEPÓS-GRADUAÇÃO EMENGENHARIAELÉTRICA E DECOMPUTAÇÃO

Especificações e Concepção de um

Front-End

UHF

Integrado Multipadrão em Tecnologia CMOS

130nm

Carlos Antonio Mendes da Costa Júnior

Orientador: Prof. Dr. Sebastian Yuri Cavalcanti Catunda Co-Orientador: Prof. Dr. Robson Nunes de Lima

Dissertação de Mestrado apresentada ao

Pro-grama de Pós-Graduação em Engenharia Elé-trica e de Computação da UFRN (área de con-centração: Automação e Sistemas) como parte dos requisitos para obtenção do título de Mes-tre em Engenharia Elétrica.

UFRN / Biblioteca Central Zila Mamede. Catalogação da Publicação na Fonte

Costa Júnior, Carlos Antonio Mendes da.

Especificações e concepções de front-end UHF integrado e multipadrão em tecnologia CMOS 130nm/ Carlos Antonio Mendes da Costa Júnior. – Natal, RN, 2014.

79 f. : il.

Orientador: Prof. Dr. Sebastian Yuri Cavalcanti Catunda. Coorientador: Prof. Dr. Robson Nunes de Lima.

Dissertação (Mestrado) – Universidade Federal do Rio Grande do Norte. Centro de Tecnologia. Programa de Pós-Graduação em Engenharia Elétrica e de Computação.

1. SBCDA – Dissertação. 2. Argos – Dissertação. 3. UHF - Dissertação. 4. LNA - Dissertação. 5. Fron-end - Dissertação. 6. CMOS - Dissertação. I. Catunda, Sebastian Yuri Cavalcanti Catunda. II. Lima, Robson Nunes de. III. Universidade Federal do Rio Grande do Norte. IV. Título.

Agradeço à minha família, principalmente aos meus pais, minhas irmãs e minha noiva por todo o apoio incondicional que sempre me deram em todos os momentos da minha vida.

Aos meus orientadores, Prof. Yuri Catunda e Prof. Robson Nunes, pelo apoio durante todo o projeto. Agradeço aos meus amigos, José Sales e a Gabriel Cunha, pelas inúmeras dis-cussões diárias e feedbacks que possibilitaram a realização desse trabalho. Agradeço aos pro-fessores Vincent Bourguet e Fernando Rangel pelos conselhos e dicas. Agradeço ainda ao meu amigo de sempre, Diego Cirilo, pela ajuda no ABNTEX.

Aos atuais e antigos membros da equipe do projeto, Prof. Vincent Bourguet, Dr. Michel Vasilevski, Dr. Nicolas Beilleau e Carlyle Câmara, pelas positivas contribuições a este projeto desafiador. Agradeço ao Dr. Diomadson Belfort, pela grande ajuda que vem dando à equipe com as ferramentas de EDA e conhecimento em RFIC.

À equipe do INPE-CRN, em especial aos engenheiros Manoel Jozeane, João Carlos Pécala Rae, José Marcelo Duarte e Marcia Barros, pelo apoio e cooperação ao longo do desen-volvimento desse projeto.

O Sistema Brasileiro de Coleta de Dados Ambientais (SBCDA) é responsável pela coleta e transmissão de dados meteorológicos e ambientais, utilizados por dezenas de instituições e organizações nacionais. O segmento espacial do sistema, composto pelos satélites de coleta de dados, é uma peça fundamental para seu funcionamento. Para garantir a continuidade e qualidade desses serviços, esforços são voltados para o desenvolvimento de alternativas para a construção de novos satélites. Visando reduzir o tamanho do atual transponder brasileiro, é proposto neste trabalho a integração de uma interface de rádio frequência (do inglês Front-End) a ser embarcado nos receptores da próxima geração dos satélites SBCDA. O circuito é concebido respeitando os requisistos do padrão de coleta de dados internacional, ARGOS, e do SBCDA. Este trabalho foca, portanto, na integração de um amplificador de baixo ruído e dois misturadores na faixa UHF em tecnologia CMOS padrão. As especificações de projeto são primeiramente descritas e então as topologias dos circuitos são escolhidas. A concepção dos circuitos é analisada e os seus parâmetros de projeto são derivados. Finalmente, seu layout é concebido e os resultados finais são divulgados. O chip será fabricado utilizando a tecnologia CMOS padrão de 130 nm da STmicroelectronics.

The Brazilian Environmental Data Collecting System (SBCDA) collects and broadcasts mete-orological and environmental data, to be handled by dozens of institutions and organizations. The system space segment, composed by the data collecting satellites, plays an important role for the system operation. To ensure the continuity and quality of these services, efforts are being made to the development of new satellite architectures. Aiming a reduction of size and power consumption, the design of an integrated circuit containing a receiver front-end is proposed, to be embedded in the next SBCDA satellite generations. The circuit will also operate under the requirements of the international data collecting standard ARGOS. This work focuses on the design of an UHF low noise amplifier and mixers in a CMOS standard technology. The specifi-cations are firstly described and the circuit topologies presented. Then the circuit conception is discussed and the design variables derived. Finally, the layout is designed and the final results are commented. The chip will be fabricated in a 130 nm technology from ST Microelectronics.

Figura 1 – Sistemas de Coleta de Dados Ambientais Baseado em Satélites. . . 18

Figura 2 – Mapas de PCDs espalhadas pelo território Brasileiro. . . 19

Figura 3 – Distribuição de frequências dos sistemas ARGOS e SBCDA. . . 21

Figura 4 – Vários estágios da Arquitetura Super-Heteródina - Utilizada no SCD. . . 24

Figura 5 – Arquitetura Baixa FI e Circuito a ser Integrado. . . 24

Figura 6 – Relação entre a figura de ruído e o SNR ao longo da cadeia RF. . . 26

Figura 7 – Ganho doFront-Endpara o sistema Argos 3 HD. . . 28

Figura 8 – Definição dos parâmetros de linearidade. . . 30

Figura 9 – ParâmetroS21 do filtro passa-banda de entrada. . . 31

Figura 10 – Níveis de potência dos bloqueadores depois do filtro de entrada. . . 31

Figura 11 – Técnicas de Projeto de LNA . . . 36

Figura 12 – Topologia Escolhida para os Estágios de Ganho do LNA. . . 37

Figura 13 – Conversor de Entrada Simples para Saída Diferencial. . . 38

Figura 14 – Misturadores Conceitual (a) e Simples (b). . . 39

Figura 15 – Misturador Ativo Duplamente Balanceado. . . 40

Figura 16 – Misturador Ativo Duplamente Balanceado com Acoplamento AC. . . 40

Figura 17 – Misturador Ativo Duplamente Balanceado com Scoplamento D e com Carga RC Melhorada porCurrent Steering. . . 41

Figura 18 – Diagrama com a Arquitetura Completa do FE em Quadratura. . . 42

Figura 19 – Design Flow. . . 43

Figura 20 – LNA Indutivo. . . 44

Figura 21 – LNA Resistivo. . . 46

Figura 22 – Conversor de Entrada Simples para Saída Diferencial. . . 47

Figura 23 – Comparação entre o Sinal de Saída Positiva e o de Saída Negativa do Con-versor. . . 48

Figura 24 – Blocos do Misturador. . . 49

Figura 25 – Estágio de Transcondutância do Misturador. . . 50

Figura 26 – Estágio de Chaveamento do Misturador. . . 51

Figura 27 – Estágio de Carga do Misturador. . . 52

Figura 28 – Buffer de Saída do Misturador. . . 53

Figura 29 – Circuito de Polarização - Transistor Conectado por Diodo. . . 54

Figura 30 – Forma de Onda de Saída doFront-Endem Nível de Esquemático . . . 55

Figura 31 – Análise de Monte-Carlo da Figura de Ruído para oFront-EndPré-layout. . 57

Figura 32 – Análise de Monte-Carlo do Ganho de Potência para oFront-EndPré-layout. 58 Figura 33 – Análise de Monte-Carlo da Perda de Retorno para oFront-EndPré-layout. . 58

Figura 37 – LayoutCompleto do LNA. . . 63 Figura 38 – Layoutdo Misturador. . . 64 Figura 39 – LayoutdoFront-EndCompleto com os Capacitores de Desacoplamento. . . 66 Figura 40 – Visualização em 3D de uma das Linhas de Transmissão utilizadas nesse

Quadro 1 – Resumo dos Protocolos de Comunicação . . . 22

Quadro 2 – Comparativo de Estado da Arte para Diferentes Arquiteturas de Receptores 25 Quadro 3 – Especificações do ADC Sigma-Delta de 4 Ordem. . . 29

Quadro 4 – Resumo dos Requisitos doFront-Endpara os Sistemas ARGOS e SBCDA. 32 Quadro 5 – Valores de Desempenho Típico para um LNA. . . 33

Quadro 6 – Resumo dos Requisitos Iniciais do LNA e do Misturador. . . 34

Quadro 7 – Resumo dos Parâmetros do LNA Indutivo. . . 45

Quadro 8 – Resumo dos Componentes Passivos do LNA Indutivo. . . 46

Quadro 9 – Resumo dos Parâmetros do LNA Resistivo. . . 47

Quadro 10 – Valor do Capacitor de Defasamento. . . 48

Quadro 11 – Comparação Numérica entre o Sinal de Saída Positiva e o de Saída Nega-tiva do Conversor. . . 48

Quadro 12 – Resumo dos Transistores do Estágio de Transcondutância. . . 51

Quadro 13 – Resumo dos Transistores do Estágio de Chaveamento. . . 52

Quadro 14 – Resumo dos Transistores do Estágio de Carga. . . 53

Quadro 15 – Resumo dos Transistores doBuffer. . . 53

Quadro 16 – Largura dos Transistores de Polarização. . . 55

Quadro 17 – Resumo dos Parâmetros de Desempenho do LNA e do Misturador em Nível de Esquemático. . . 56

Quadro 18 – Resumo dos Parâmetros de Desempenho doFront-End. . . 56

Quadro 19 – Resumo dos Parâmetros de Desempenho do LNA e do Misturador em Nível de Esquemático. . . 57

Rb: Taxa de Bits por Segundo

Rc: Taxa de Chips por Segundo

SNRin: Relação Sinal-Ruído de Entrada

SNRout: Relação Sinal-Ruído de Saída

VDS: Drain-Source Voltage

VGS: Gate-Source Voltage

VOV: Overdrive Voltage

VT H: Threshold Voltage

Vswing: Signal Swing Voltage

β: Fator deroll-off do Filtro Gaussiano

τ: Eficiência Espectral

iCP1dB: Compression point 1dB

ADCmargem: Margem de 10 dB Acima do Ruído de Quantização

ADCruido: Ruído de Quantização do ADC

Aruido: Ruído de Entrada do LNA Amplificado

Escdinamica: Escala Dinâmica do ADC

GMAX: Ganho Máximo Suportador peloFront-End

Pbloq: Potência do Bloqueador mais Forte

Pruido: Potência do Ruído Térmico

Psat: Nível de Saturação do Sistema

Re fdBm: Nível de Referência do ADC

ADC: Analog to Digital Converter

ARGOS: Advanced Research and Global Observation Satellite

CBERS: China-Brazil Earth Resources Satellite

CBERS: China–Brazil Earth Resources Satellite

CI: Circuito Integrado

CNES: Centre National d’Etudes Spatiales

CNM: Classical Noise Matching

CONASAT: Constelação de Nanossatélites Ambientais

FE: Front-End

GMSK: Gaussian Minimum Shift Keying

HD: High Data Rate

INPE-CRN: Instituto Nacional de Pesquisas Espaciais - Centro Regional do Nordeste

INPE: Instituto Nacional de Pesquisas Espaciais

IP3: Third-order intercept point

LD: Low Data Rate

LNA: Low Noise Amplifier

LO: Local Oscillator

NASA: National Aeronautics and Space Administration

NF: Noise Figure

NG: High Sensibility Service

NOAA: National Oceanic and Atmospheric Administration

NRZ: Non-Return-to-Zero

PCDs: Plataformas de Coleta de Dados

PCNO: Power-Constrained Noise Optimization

PI: Perda de Inserção

PLL: Phase Locked Loop

SCD: Satélites de Coleta de Dados

SCDABS: Sistemas de Coleta de Dados Ambientais Baseado em Satélites

SH: Super-Heteródina

SINDA: Sistema Integrado de Dados Ambientais

SNIM: Simultaneous Noise and Input Matching

STD: Standard Service

1 INTRODUÇÃO . . . . 16

1.1 Delineamento desse Trabalho . . . 16

2 CONTEXTUALIZAÇÃO . . . . 17

2.1 Introdução . . . 17

2.1.1 ARGOS. . . 17

2.1.2 SBCDA . . . 18

2.2 Protocolos de Comunicação . . . 19

2.2.1 ARGOS. . . 20

2.2.2 SBCDA . . . 20

2.3 Motivação . . . 22

2.4 Estado da Arte . . . 23

2.5 Principais Contribuições . . . 25

3 REQUISITOS DE PROJETO . . . . 26

3.1 Figura de Ruído doFront-End . . . 26

3.2 Ganho doFront-End . . . 28

3.3 Linearidade doFront-End . . . 30

3.4 Frequência Intermediária doFront-End . . . 31

3.5 Resumo dos Requisitos doFront-End . . . 32

3.6 Requisitos do LNA e do Misturador . . . 32

3.6.1 Figura de Ruído . . . 32

3.6.2 Ganho . . . 33

3.6.3 Linearidade. . . 33

3.7 Resumo dos Requisitos do LNA e do Misturador . . . 34

4 TOPOLOGIAS . . . . 35

4.1 Amplificador com Baixo Ruído . . . 35

4.1.1 Técnica CNM -Classical Noise Matching . . . 35

4.1.2 Técnica SNIM -Simultaneous Noise and Input Matching . . . 35

4.1.3 Técnica PCNO -Power-Constrained Noise Optimization . . . 36

4.1.4 LNA Indutivo Escolhido . . . 36

4.1.5 LNA Resistivo Escolhido . . . 36

4.1.6 Conversor de Entrada Simples para Saída Diferencial . . . 37

4.2 Misturador . . . 38

4.2.4 Misturador Escolhido . . . 41

4.3 Arquitetura Final doFront-End . . . 42

5 CONCEPÇÃO . . . . 43

5.1 Amplificador com Baixo Ruído . . . 44

5.1.1 LNA com Terminação Indutiva . . . 44

5.1.2 LNA com Terminação Resistiva . . . 46

5.2 Conversor de Entrada Simples para Saída Diferencial . . . 47

5.3 Misturador . . . 49

5.3.1 Estágio de Transcondutância (ET) . . . 50

5.3.2 Estágio de Chaveamento (ECh) . . . 51

5.3.3 Estágio de Carga (ECa) . . . 52

5.3.4 Buffer de Saída . . . 53

5.4 Circuitos de Polarização . . . 54

5.4.1 Resultados da Simulação doFront-End . . . 54

5.5 Variação do Processo . . . 56

6 LAYOUT . . . . 59

6.1 Amplificador de Baixo Ruído . . . 59

6.2 Conversor de Entrada Simples para Saída Diferencial . . . 61

6.3 LNA Completo. . . 62

6.4 Misturador . . . 63

6.5 Layout Completo . . . 65

7 RESULTADOS . . . . 68

7.1 Front-End Completo . . . 68

8 CONCLUSÃO . . . . 71

Referências . . . . 73

APÊNDICE A – INFORMAÇÕES ADICIONAIS . . . . 78

1 Introdução

O monitoramento de ambientes remotos é feito principalmente por auxílio de satélites. Adquirindo dados por sensoriamento remoto ou através de uma conexão com plataformas lo-cais, esses satélites compartilham as informações retiradas da região de interesse com uma base terrestre. Devido à crescente necessidade de ampliação do atual sistema Brasileiro de coleta de dados ambientais, um projeto de uma constelação de nanossatélites foi proposto (CARVA-LHO et al., 2012). Contudo, a filosofia de projeto desses dispositivos prevê, dentre outras, uma alta integração de seus sistemas, condição essa que não pode ser atendida pelo presente trans-ponder de coleta de dados utilizado nos satélites Brasileiros, já que é ele feito totalmente com componentes discretos.

Nesse trabalho, portanto, uma metodologia dedesigndeFront-Endintegrado é introdu-zida. Isso favorece a utilização de um componente de alta densidade de funções em um futuro

transponder embarcado em nanossatélites de coleta de dados ambientais. EsseFront-End será desenvolvimento em tecnologia CMOS padrão 130 nm com arquitetura baixa-FI em quadratura.

1.1 Delineamento desse Trabalho

A seguir, é exposto um breve delineamento de cada capítulo que compõe esse trabalho.

No Capítulo 2, as motivações e objetivos desse trabalho são expostos. Nele também é

apresentada uma visão geral dos sistemas ARGOS e SCBDA.

No Capítulo 3, uma derivação cuidadosa dos requisitos mínimos necessários para um

receptor multi-padrão integrado é feita.

No Capítulo 4, uma revisão de arquiteturas de receptores é realizada. Ao seu fim, as

topologias mais adequadas a essa aplicação são escolhidas.

No Capítulo 5, é elaborada uma análise detalhada dos circuitos a nível de transistores,

bem como o que motivou seus pontos de operação.

NoCapítulo 6, as principais soluções e técnicas utilizadas nolayoutdesse circuito

inte-grado são apresentadas.

No Capítulo 7, os resultados de desempenho das simulações pós-layout são exibidos e

uma comparação com o estado da arte deFront-Endsé realizada.

Finalmente, noCapítulo 8é feita uma análise dos resultados desse trabalho e

2 Contextualização

Neste capítulo apresenta-se a aplicação que motivou o atual trabalho. Primeiramente, são mostrados detalhes do funcionamento e protocolos de comunicação dos sistemas no qual esse trabalho está inserido. Em sequência, são apresentados a motivação e um breve estado da arte de receptores. E, finalmente, a proposta desse trabalho é exposta, reiterando o objetivo geral e os específicos.

2.1 Introdução

O monitoramento do estado ecológico global é estabelecido basicamente de duas for-mas, por sensoriamento remoto ou por mediçãoin-situ (GINARI, 1992). O sensoriamento re-moto é realizado por sensores acomodados a bordo de satélites ou aeronaves, não tendo con-tato, dessa forma, com o local a ser monitorado. Já a medição in-situ, como o nome sugere, apresenta sensores posicionados no próprio local onde se deseja medir as variáveis ambientais. Esses sensores estão instalados em plataformas autônomas que enviam as informações adquiri-das do ambiente para uma estação central por meio de satélites repetidores de sinal. Apesar de ambos os métodos fornecerem um importante meio nos estudos climatológicos e de proteção ambiental, esse trabalho está inserido no contexto de medições ambientaisin-situ.

Os Sistemas de Coleta de Dados Ambientais Baseados em Satélites (SCDABS) são os casos mais comuns do monitoramento ecológico in-situ. Esse sistema é constituído de três segmentos principais, sendo um espacial e dois terrestres. Uma constelação de satélites forma o segmento espacial, enquanto que a estação terrestre de recepção e as Plataformas de Coleta de Dados (PCDs) formam os segmentos terrestres. Cada segmento é bastante complexo e composto por vários subsistemas, que juntos formam uma cadeia de distribuição de dados. Como retratado na Figura 1, esse laço de comunicação se desenvolve da seguinte forma. As PCDs reúnem um conjunto de sensores que captam dados sobre o ambiente no qual elas estão inseridas. Esses dados são processados e transmitidos pelas PCDs para os Satélites de Coleta de Dados (SCD). Ao chegar no SCD, o sinal emitido pelas PCDs é tratado e enviado de volta para a estação terrestre de recepção através de um subsistema chamado de transponder (repetidor de sinais). Finalmente, a estação de recepção demodula e distribui as informações ambientais para os mais diversos usuários.

2.1.1 ARGOS

Figura 1 – Sistemas de Coleta de Dados Ambientais Baseado em Satélites.

partir de um memorando de entendimento entre o Centre National d’Etudes Spatiales(CNES, Agência Espacial Francesa), oNational Aeronautics and Space Administration(NASA, Agên-cia EspaAgên-cial Estadunidense) e o National Oceanic and Atmospheric Administration (NOAA, Administração Oceânica e Atmosférica Estadunidense).

O sistema ARGOS coleta, processa e dissemina os dados ambientais obtidos de pla-taformas fixas e móveis espalhadas por todo o globo. Além disso, o sistema também provê a localização geográfica do transmissor em qualquer lugar da Terra através de medições do efeito Doppler. Essa tecnologia, por sua vez, permitiu aos biólogos estudar oroamingde animais sel-vagens, revolucionando a pesquisa de mamíferos marinhos (MORELLE, 2007). Atualmente, o ARGOS 3 está em pleno funcionamento e apresenta 3 categorias deuplinkde dados, a categoria

Low Data Rate(LD), que é subdividida emStandard Service(STD) e High Sensibility Service

ou Low Power (NG), e o High Data Rate (HD) (EOPORTAL. . . , 2014). A quarta versão do sistema ARGOS, a qual está sendo preparada pelo CNES, trará uma banda dedicada à aplicação de baixa potência (UCSD-. . . , 2014).

A sua importância global fica clara quando são observados alguns números do sistema. O segmento espacial do sistema ARGOS conta com oito satélites, sendo quatro para o sistema ARGOS 2 e os outros quatro para o ARGOS 3. Seu segmento terrestre apresenta mais de 21.000 plataformas catalogadas em 2013 e 60 estações terrenas espalhadas por todo o mundo (ARGOS-SYSTEM, 2013).

2.1.2 SBCDA

O SCBDA, apesar de apresentar números mais singelos quando comparados com o ARGOS, vem demonstrando importante papel para a pesquisa e o desenvolvimento do país. O sistema pode ser usado para diversas aplicações, entre elas as relacionadas aos seguintes tópicos: hidrologia, meteorologia, oceanografia, química da atmosfera, defesa civil, monitoramento de níveis de reservatórios de água, entre outros (YAMAGUTI, 2009). Além disso, ele possibilita também o rastreamento de animais no caso de plataformas móveis.

Os satélites SCD 1, SCD 2 e CBERS 2 compõem o segmento espacial do SBCDA, enquanto que a estação receptora de Cuiabá, de Alcântara e o Centro de Controle da Missão formam o segmento terrestre de comando e recepção. Os dados recebidos pelas estações terrenas são enviados ao Sistema Integrado de Dados Ambientais (SINDA), em funcionamento no INPE-CRN de Natal, para então serem processados, armazenados e distribuídos aos usuários finais (SINDA. . . , 2014). O outro segmento terrestre é formado pelas 800 PCDs espalhadas por todo o território nacional e mostradas na Figura 2.

Figura 2 – Mapas de PCDs espalhadas pelo território Brasileiro.

Fonte: http://sinda.crn2.inpe.br/PCD/

2.2 Protocolos de Comunicação

A fim de respaldar o Capítulo 3, uma breve descrição dos protocolos utilizados nos

2.2.1 ARGOS

Como já comentado, o ARGOS 3 apresenta três categorias deuplinkde dados, oLow Data Rate(LD), que é subdividido emLow Power(NG) eStandard(STD) e oHigh Data Rate

(HD).

As categorias NG e STD apresentam uma taxa de 400 bit/s, mas são codificadas e mo-duladas de forma diferente. O LD STD apresenta uma codificação de linha do tipo Manchester NRZ com esquema de modulação BPSK. O LD NG, por outro lado, apresenta uma codifica-ção de canal do tipo Convolutional(7, 1/2) e é modulado em QPSK. Ambas as categorias são centradas em 401,650 MHz e compartilham uma banda de 80 kHz ao redor da portadora, su-ficiente para garantir o recebimento pelo transponder de várias PCDs simultaneamente. Cada PCD transmite seu sinal em uma banda de 1,0 kHz (STD) ou 500 Hz (NG), que é recebido pelo satélite com uma potência máxima para ambas as categorias de -114 dBm e mínimas de -137 dBm para o LD NG e de -123 dBm para o STD (EOPORTAL. . . , 2014).

A categoria HD, por sua vez, apresenta uma taxa de 4800 bits/s, um codificação de canal do tipo Convolutional(7, 3/4) e é modulada em GMSK. A banda do sinal está centrada em 401,595 MHz com uma largura de banda de 30 kHz. O sinal transmitido pela plataforma HD apresenta uma banda de 12,8 kHz, que é recebido pelo satélite com uma potência máxima de -108 dBm e mínima de -123 dBm (EOPORTAL. . . , 2014).

Antes de avançar, é interessante esclarecer os seguintes tópicos.

• A codificação de linha do Argos LD e do SBCD aumenta as suas taxas de bits em 2 vezes (deixando-os com uma taxa de chip de 800 bits/s);

• A codificação de canal do Argos NG aumenta a sua taxa de bits também em 2 vezes, enquanto que no Argos HD a taxa de bits sofre um aumento de 4/3 (deixando-o com uma taxa de chip de 6400 bits/s).

• Devido à eficiência espectral, a modulação também é um ponto importante nos cálculos de requisitos e será comentada com mais detalhes no Capítulo 3;

• Sabendo que as bandas do HD e do LD estão lado a lado, logo a largura de banda total das duas categorias é de 110 kHz centrada em 401,635 MHz como mostrado na Figura 3.

2.2.2 SBCDA

O Sistema Brasileiro de Coleta de Dados foi baseado no ARGOS e, portanto, exibe características muito similares aos da categoria LD do ARGOS 3.

permite que o sinal apresente uma portadora residual, o que facilita a sua detecção e demodu-lação. Centrado na frequência de 401,635 MHz e com uma largura de banda de 120 kHz (10 kHz a mais que o ARGOS 3), o SBCDA é dividido em 4 sub-bandas, chamadas de INPE 1, INPE2, INPE 3 e INPE 4 (mostrados na Figura 3) permitindo que até 8 PCDs sejam recebidas simultaneamente sem interferências (TIKAMI et al., 2012). Cada PCD transmite um sinal com uma largura de 1,0 kHz, que é recebido pelo satélite com uma potência máxima de -98 dBm e mínima de -123 dBm (EOPORTAL. . . , 2014).

Finalmente é possível verificar na Figura 3 que os sistemas SBCDA e ARGOS 3 têm suas bandas de operação superpostas e centradas em 401,635 MHz. O Quadro 1 contém o resumo de todas as informações dos protocolos de comunicação discutidas até o momento. Dentre todos os parâmetros apresentados no quadro, destacam-se:

• Ambos os sistemas apresentam um requisito deBER(Bit Error Rateou Taxa de Erro de Bits) de 10−5.

• Sensibilidade de um receptor é definida como a potência mínima do sinal de entrada necessária para produzir, após a demodulação, uma taxa de erro de bit específica.

• Máxima Potência Rxé o maior valor de potência do sinal recebido na antena do satélite.

• Banda Rxé a largura de banda necessária para acomodar todos as PCDs daquele padrão recebidas pelo satélite.

• Banda da PCD é referente à banda do sinal que corresponde à 85% da potência total contida no seu espectro (RAE, 2005).

Quadro 1 – Resumo dos Protocolos de Comunicação

Parâmetros SCBD ARGOS-3 ARGOS-3 HD

STD NG

Sensibilidade -123 dBm -123 dBm -137 dBm -123 dBm

Potência Máxima Rx -98 dBm -114 dBm -114 dBm -108 dBm

Freq. da Portadora 401.635 MHz 401.650 MHz 401.650 MHz 401.595 MHz

Banda Rx 120 kHz 80 kHz 80 kHz 30 kHz

Taxa de Bits 400 bps 400 bps 400 bps 4800 bps

BER 10−5 10−5 10−5 10−5

Codificação de Linha Manchest. NRZ Manchest. NRZ – –

Codificação de Canal – – Conv. (7,1/2) Conv. (7,3/4)

Taxa de Chips 800 bps 800 bps 800 bps 6400 bps

Modulação PCM/PM/±60 ° BPSK QPSK GMSK

Banda da PCD 1000 Hz 1000 Hz 500 Hz 1920 Hz

2.3 Motivação

Nos últimos anos tem havido um interesse crescente no uso de nanossatélites na mais di-versas áreas da pesquisa espacial (BLACKWELL et al., 2012; MARIN, 2012; SWARTWOUT, 2007). Seguindo, então, uma tendência mundial, o Instituto Nacional de Pesquisas Espaciais -Centro Regional do Nordeste (INPE-CRN) lançou uma proposta para garantir a continuidade do SINDA e para capacitar especialistas por meio de uma Missão Espacial para Coleta de Da-dos Ambientais baseada em uma Constelação de Nanossatélites (CONASAT) (CARVALHO et al., 2012). Devido ao pequeno tamanho dos nanossatélites (10 cm3), a sua carga útil deverá ser uma versão reduzida do atualtransponder(256 mm x 210 mm x 105 mm). Essa versão será ob-tida através da utilização de circuito integrado de propósito específico, que apresenta umdesign

mais compacto e confiável do que ostransponderstotalmente discretos utilizados atualmente.

Contudo, o projeto de dispositivos eletrônicos para aplicações espaciais apresentam uma série de restrições e desafios dedesign. O primeiro deles envolve a distância do enlace de comu-nicação (750 km, nesse caso). O sinal atravessa um canal de elevada atenuação, que fragiliza-o e deixa-o susceptível a uma grande quantidade de sinais interferentes. O aumento da potência do sinal de transmissão do satélite poderia resolver parcialmente esse problema, se não fosse outro desafio inerente às aplicações espaciais, o limite de energia a bordo do satélite. Além disso, existe a radiação cósmica que causa danos ao funcionamento de circuitos digitais. A proteção contra radiação cósmica em circuitos integrados analógicos é, no entanto, um assunto pouco abordado na literatura e será inicialmente desconsiderada nesse trabalho, uma vez que a filo-sofia do projeto de nanossatélites já prevê o uso de componentes não robustos a radiação, pois agiliza sua construção e garante um bom custo-benefício (UNDERWOOD; RICHARDSON; SAVIGNOL, 2002).

caso de receptores embarcados é importante ainda que o projeto possa oferecer uma boa sensi-bilidade e uma boa seletividade. Em outras palavras, que o sistema consiga trabalhar com sinais de baixa potência em um ambiente com a presença de sinais interferentes e consumindo pouca energia.

A energia elétrica consumida peloFront-Endé consideravelmente menor que a do Back-End. Logo, o projeto de um receptor que atenda os requisitos do sistema sem empenhar-se em atingir um consumo na casa de alguns miliwatts, pode ser considerado um bom compromisso.

Finalmente, o objetivo geral dessa dissertação é o de desenvolver umFront-End inte-grado em tecnologia CMOS padrão 130 nm da STMicroelectronics, que atenda os requisitos nacionais do SBCDA e, por generalização, os do sistema internacional ARGOS, permitindo a redução do tamanho dotranspondera ser embarcado em nanossatélites.

2.4 Estado da Arte

Um transponder é um dispositivo de comunicação bidirecional que tem o objetivo de reunir sinais sobre uma variedade de frequências de uplink (da PCD para o satélite) e retransmiti-los em uma banda diferente de frequência de downlink(do satélite para a estação terrena de recepção), comumente, sem mudar o conteúdo do sinal. Para isso, o sinal deve ser apropriadamente processado através de filtragens, amplificações e translações na frequência. Dependendo dos métodos usados e da sequência de passos realizados, diferentes arquiteturas podem ser utilizadas para o receptor e o transmissor. Como, entretanto, esse trabalho concentra seus esforços na recepção do sinal, essa seção traz um breve comparativo das três principais arquiteturas de receptores, o super-heteródino, a de conversão direta e a de frequência interme-diária (MARIN, 2012).

Antes mesmo da integração de sistemas de radio frequência se tornar popular, a arqui-tetura Super-Heteródina (SH) já era a mais utilizada. Essa é a arquiarqui-tetura empregada nos atuais

transponders dos SCDs brasileiros e que está em uso desde 1993. À época, essa arquitetura foi a melhor opção para alcançar os requisitos de sensibilidade e seletividade exigidos pelo sis-tema, ao custo de um consumo de energia moderado. Seu ótimo desempenho é obtido através dos vários estágios de conversão de frequência, filtragem e amplificação experimentados pelo sinal (Figura 4). Entretanto, essa numerosa quantidade de etapas e a necessidade de filtros vo-lumosos que eliminem a frequência imagem e as componentes geradas pela etapa de conversão dificultam sua total integração em chip (SHAEFFER; LEE, 1999).

A fim de tentar resolver esses problemas de integração, arquiteturas como a Baixa-Frequência Intermediária (Baixa-FI) e a Baixa-Frequência Intermediária-Zero (Zero-FI) podem ser utilizadas.

Figura 4 – Vários estágios da Arquitetura Super-Heteródina - Utilizada no SCD.

Isso forneceria, portanto, a solução mais adequada, não fossem seus problemas com o offset

DC e com o ruídoflicker, limitações inerentes ao fato dessa arquitetura transladar o sinal banda base para a frequência zero (SHI, 2008).

Por último, a arquitetura Baixa-FI (Figura 5) também fornece uma integração total com baixo custo e baixo consumo, e ainda evita os problemas com ooffsetDC e com o ruídoflicker

dos receptores Zero-FI. Permite-se, além disso, que a frequência imagem possa ser cancelada por meio de um receptor BFI em quadratura. Essa vantagem, no entanto, deve ser utilizada com muita atenção uma vez que requer uma otimização no casamento dos canais em fase e quadratura (ELLINGER, 2007).

A fim de garantir uma total integração doFront-End, com bom desempenho de ruído e boa rejeição de imagem, a arquitetura Baixa FI em quadratura foi a escolhida para o de-senvolvimento desse trabalho. O pontilhado da Figura 5 destaca os circuitos do Low Noise Amplifier(LNA) e dos Misturadores, componentes a serem projetados, simulados e desenhados no decorrer desse trabalho. Vale ainda salientar que o Oscilador Local (LO) está em fase de desenvolvimento (COSTAJR et al., 2014) por integrantes do Laboratório de Instrumentação e Microeletrônica da UFRN.

Figura 5 – Arquitetura Baixa FI e Circuito a ser Integrado.

Quadro 2 – Comparativo de Estado da Arte para Diferentes Arquiteturas de Receptores

Arquiteturas do Receptor Super-Heteródino Conversão Direta Baixa - FI

Referência a b c

Frequência de Operação[GHz] 2.4 2.4 2.4

Ganho Global [dB] 50 30 26.3

Consumo de Energia[mW] 6.25 1.8 3.34

Tecnologia[µm] 0.25 0.18 0.13

a (ZOLFAGHARI; RAZAVI, 2003) b (NGUYEN et al., 2014)

c (PIETRON et al., 2014)

2.5 Principais Contribuições

Com base nas informações anteriores, o objetivo geral dessa dissertação é o de desen-volver um Front-End integrado em tecnologia CMOS padrão 130 nm da STMicroelectronics, que atenda, ao mesmo tempo, os requisitos do SBCDA e os do sistema internacional ARGOS.

As contribuições especificas desse trabalho são enumeradas abaixo.

1. Criação de especificações únicas que atendam a umFront-Endmultipadrão;

2. Diminuir o tamanho, mas manter, ou melhorar, o desempenho dos atuais transpon-ders.

Redução de 500 cm2(25,6 x 21,0 cm) para um chip de alguns mm2;

3 Requisitos de Projeto

Uma vez que os protocolos de comunicação foram detalhados e a arquitetura do receptor definida, esse capítulo expõe os cálculos de requisitos doFront-End. São derivados a figura de ruído, o ganho e a linearidade necessários para que o receptor atenda todas as especificações dos protocolos apresentados. Apesar dos parâmetros finais considerarem o pior caso de cada protocolo, os requisitos finais derivados aqui são feitos somente para o caso mais complexo, o ARGOS 3 HD, os outros podem ser derivados por semelhança.

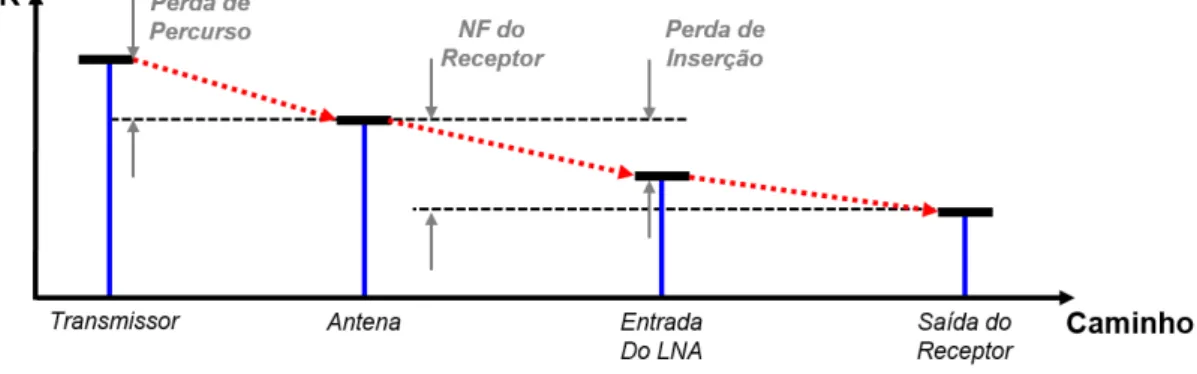

3.1 Figura de Ruído do

Front-End

A figura de ruído (Noise Figure- NF) é uma medida de degradação da relação sinal-ruído causada por um bloco na cadeia do sinal de rádio frequência (Figura 6). Em outras pala-vras, é a diferença entre a relação sinal-ruído da entrada (SNRin) e a relação sinal-ruído da saída

(SNRout), como descrito abaixo (ELLINGER, 2007):

NFdB=SNRin|dB−SNRout|dB. (3.1)

OSNRinpode ser calculado pela relação entre a menor potência do sinal de entrada do

sistema (Pinmin= -123 dBm) e a potência do ruído térmico para a banda do sinal, como mostrado

na Equação (3.2) (DESSOUKY; RAGAI; HAFEZ, 2009). Considera-se ainda uma margem de 1,5 dB para as perdas de inserção (PI) devido ao switchde redundância (1 dB) e ao filtro de entrada (0,5 dB), ambos externos ao chip.

SNRin|dB=Pin|min|dBm−PIdB−10 log(kT/10−3)−10 log(B/10−3). (3.2)

Sendoka constante deBoltzmann(1,38×10−23J/K),Ta temperatura ambiente emKelvin(pior

caso de 373 k) e Ba banda do sinal. Antes de prosseguir, no entanto, é necessário esclarecer a relação entre o efeito da modulação e da codificação de canal na banda efetiva do sinal.

A eficiência espectral é a relação entre a taxa de chips (Rc) e a banda do sinal

(Equa-ção (3.3)). Como aRcdepende ainda da codificação utilizada (Equação (3.4)), a banda do sinal

pode, então, ser derivada a partir da combinação desses dois parâmetros (Equação (3.5)) (MA-RAL; BOUSQUET, 2002).

Para exemplificar, considere a categoria ARGOS 3 HD. Esse sinal apresenta uma codi-ficação de canal do tipoConvolutional(7, 3/4), que reduz a eficiência espectral em 3/4, e uma modulação GMSK, que aumenta a eficiência espectral emN/1+β(onde N é o número de bits por símbolos eβé fator deroll-off do filtro gaussiano). Portanto, pode-se constatar abaixo, que a banda efetiva do ARGOS 3 HD é simplesmente a divisão da taxa de bits (Rb) pela multiplicação

do fator deroll-off e a eficiência espectral,

τGMSK =Rc/B=N/1+β, (3.3)

ρ=Rb/Rc, (3.4)

B= (Rb)/(ρ×τGMSK). (3.5)

Logo, considerando um fator deroll-off β= 0,5 e oConvolutional(7, 3/4), a banda total do sinal HD é dado pela Equação (3.6).

B= (4800)/((3/4)×(2/(1+0,5))) =4800 kHz. (3.6)

À luz do que foi dito, oSNRin pode ser finalmente calculado na Equação (3.7).

SNRin|dB=−123−1,5−10 log(1,38×10

−23×323

10−3 )−10 log(

1920×103

10−3 ) =12,2 dB. (3.7)

OSNRouté calculado considerando a energia por bit sobre densidade de ruído (Eb/N0)1

da modulação GMSK necessária para garantir um BERde 10−5, a banda do sinal e ainda uma

margem de segurança de 0,5 dB (Equação (3.8)) (DESSOUKY; RAGAI; HAFEZ, 2009).

SNRout|dB= (Eb/N0)dB−10 log(Rb/B) +Margem, (3.8a)

SNRout|dB=5,2−10 log(4800

4800) +0,5=5,7 dB. (3.8b)

1 Valor deE

Por fim, a figura de ruído do Front-End para a categoria ARGOS 3 HD pode ser di-retamente calculada por substituição dos valores da relação sinal ruído de entrada e saída na Equação (3.1), repetida abaixo,

NFdB=SNRin|dB−SNRout|dB=12,2−5,7=6,5 dB. (3.9)

O valor encontrado na Equação (3.9) significa que se oFront-End apresentar um NF menor do que 6,5 dB, o sinal apresentará um BER de no máximo 10−5após a sua demodulação.

3.2 Ganho do

Front-End

Para facilitar a explicação do cálculo de ganho doFront-End, considere a Figura 7. São apresentados na barra à esquerda dessa figura os níveis de potência na entrada do LNA. De baixo para cima tem-se, consecutivamente, a potência do ruído térmico (Pruido), a menor potência do

sinal (Pin|min), a do bloqueador mais forte (Pbloq) e o nível de saturação do sistema (Psat). Já na

barra à direita vê-se os níveis de potência referentes à entrada do Conversor Analógico Digital (Analog to Digital Converter - ADC). De baixo para cima tem-se, consecutivamente, o ruído de quantização do ADC (ADCruido), o ruído de entrada do LNA amplificado (Aruido), a menor

potência do sinal amplificado (Ain|min) e o nível de referência do ADC (Re fdBm). A seta em azul representa a amplificação oferecida pelo FE. Logo, é possível verificar que o ganho do FE pode ser calculado de forma a ajustar o sinal de entrada de menor potência (Pin|min) ao nível mínimo da escala dinâmica do ADC (Escdinamica), respeitando a relação sinal ruído de saída (Ain|min).

Isso assegura que o sinal alcance oSNRout necessário na entrada do ADC para garantir o BER

de 10−5e otimiza a excursão do sinal para a escala do ADC.

As especificações do ADC considerado nesse design são mostradas no Quadro 3. A partir delas pode-se extrair o nível de ruído do conversor aplicando a fórmula do ruído de quan-tização (DESSOUKY; RAGAI; HAFEZ, 2009).

ADCruido|dBm=Re fdBm−n×6,02+1,76, (3.10a)

ADCruido|dBm=−5,2−16×6,02+1,76=-103,25 dBm. (3.10b)

A fim de se obter o nível mínimo de potência do sinal na entrada do ADC, considera-se uma margem de 10 dB (ADCmargem) acima do ruído de quantização e adiciona-se o SNRout

necessário para a correta demodulação do sinal. A partir da diferença desse valor com a potência mínima do sinal na entrada do LNA, pode-se calcular o ganho mínimo requerido pelo FE como se segue:

GdB=ADCruido|dBm+ADCmargem+SNRout|dB−Pin|min, (3.11a)

GdB=−103,25+10+5,7−(−124,5)≈37 dB. (3.11b)

Após a sua obtenção, o valor de ganho do FE pode ser adicionado à potência de ruído térmico na entrada do LNA e à figura de ruído esperado pelo FE a fim de validar a margem de 10 dB inicialmente empregada (seta cinza mais abaixo da Figura 7). O nível de saturação do sistema pode ser diretamente encontrado pela subtração do nível de referência do ADC (Re fdBm) pelo ganho encontrado (37 dB), como mostrado pela seta laranja da Figura 7.

O ganho máximo do FE pode ser derivado a partir da diferença entre o nível de refe-rência do ADC e o bloqueador de maior potência na entrada do LNA (GMAX = 79,8 dB), como

demonstrado pela seta cinza mais acima da Figura 7.

Quadro 3 – Especificações do ADC Sigma-Delta de 4 Ordem.

Resolução 16 bits

Nível de Referência -5,2 dBm

Ruído de Quantização -103,25 dBm

Largura de Banda 40 MHz

Frequência Central 22 MHz

Impedância de Entrada 2 kΩ

3.3 Linearidade do

Front-End

Os blocos do Front-End, como o LNA e os misturadores, apresentam um comporta-mento não-linear inerente, tornando a relação entrada/saída não-linear a partir de um certo valor de potência de entrada. Tais não-linearidades geram intermodulações, e deve-se atentar ao fato que a produtos dessa intermodulação possam cair na banda do sinal desejado, podendo assim saturar aqueles blocos do FE.

O Ponto de Compressão a 1 dB (CP1dB) é definido como a condição em que seu sinal de

saída apresenta um desvio de 1 dB do valor de potência que teria se tivesse um comportamento puramente linear (RAZAVI, 1997).

Uma outra medida de linearidade muito utilizada é o ponto de intercepção de terceira or-dem (IP3), onde a potência fundamental do sinal RF cruza-se com o produto de intermodulação de terceira ordem (IM3) (LEE, 2004). A Figura 8 ilustra o conceito desses parâmetros.

Figura 8 – Definição dos parâmetros de linearidade.

A Figura 9 mostra os parâmetroS21 eS11 do filtro passa-banda na entrada do receptor

(MONOLITHICS, 2008), e na Figura 10 encontram-se os bloqueadores presentes depois da-quele filtro. Para achar a potência de entrada referente aoCP1dBdo FE, parte-se do pressuposto

que o receptor suporta a potência dos bloqueadores sem saturar. Considerando agora o bloque-ador mais forte depois do filtro (Pbloq|max= -84,45 dBm em 462 MHz)2, subtrai-se 1 dB do seu nível de potência para encontrar o ponto de compressão da entrada a 1 dB. Acrescentando ainda uma margem de segurança de 3 dB, oiCP1dBpode ser calculado como:

iCP1dB=Pbloq|max+3−1= - 82,4 dBm. (3.12) 2 Vale salientar, no entanto, que este bloqueador só está presente nos satélites CBERS (China–Brazil Earth

Deriva-se, então, a potência de entrada referente ao IP3 a partir da seguinte equação (RAZAVI, 1997):

IIP3dB=iCP1dB+9,6=- 72,8 dBm. (3.13)

Apesar de baixo, esse valor deve ser considerado, pois o ganho do FE é relativamente alto (49 dB) e sinais interferentes de baixa potência podem lever o LNA a saturação.

Figura 9 – ParâmetroS21 do filtro passa-banda de entrada.

Fonte: Figura extraída a partir da medição do filtroSAW RF1419D da Murata.

Figura 10 – Níveis de potência dos bloqueadores depois do filtro de entrada.

Fonte: Retirado do (ESPACIAIS, 2013).

3.4 Frequência Intermediária do

Front-End

Essa arquitetura de PLL oferece como o sinal de saída uma frequência múltipla inteira da refe-rência. Logo, escolhe-se uma frequência de 420 MHz para o oscilador local, que ao realizar a conversão com o sinal RF em 401,635 MHz, gera uma frequência intermediária fIF = 18,365

MHz, dentro da banda do conversor A/D.

3.5 Resumo dos Requisitos do

Front-End

Os parâmetros para as outras categorias são resumidos no Quadro 4 e o procedimento de cálculo é idêntico ao utilizado no ARGOS 3 HD. A última coluna apresenta o pior caso de cada parâmetro. Estes valores são os requisitos finais do receptor multi-padrão, que atende simultaneamente as especificações do ARGOS 3 e do SBCDA.

Quadro 4 – Resumo dos Requisitos doFront-Endpara os Sistemas ARGOS e SBCDA.

Parâmetros SBCD Argos 3 STD Argos 3 NG Argos 3 HD Final

NF FE (dB) 11,00 11,00 4,30 6,50 4,30

Gain (dB) 39,30 39,30 49,00 41,00 49,00

Sensibilidade (dBm) -124,50 -124,50 -138,50 -124,50 -138,50 Max. Input (dBm) -99,50 -115,50 -115,50 -109,50 -99,50

Sinal BW (Hz) 1000 1000 500 1920

-iCP1 (dBm) -82,50 -82,50 -82,50 -82,50 -82,50

IIP3 (dBm) -72,90 -72,90 -72,90 -72,90 -72,90

3.6 Requisitos do LNA e do Misturador

A abordagem para a derivação dos requisitos do LNA e do Misturador é a seguinte. Como nesse estágio do trabalho nenhum dos dois blocos foram desenvolvidos, o design do LNA é realizado para atingir ou superar características típicas apresentadas no Quadro 5, onde

Av é o ganho de tensão e Pdis, a potência dissipada. Considerando-se, então, esses requisitos

como alcançáveis para o projeto de um amplificador, os requisitos do misturador são derivados diretamente deles. Ao final do Capítulo 5, que trata sobre concepção desses circuitos, uma análise global, envolvendo ambos os componentes, é realizada a fim de verificar a adequação de seus desempenhos com os requisitos doFront-Endretirados nesse capítulo.

3.6.1 Figura de Ruído

Em um sistema com N blocos cascateados, o fator de ruído total pode ser dado pela equação (ELLINGER, 2007):

Quadro 5 – Valores de Desempenho Típico para um LNA.

S11 -21 dB Av 80 dB

S21 80 dBa P1dB -84 dBmb

NF 2,1 dB Pdis 22mW

Fonte: (HUANG et al., 2003).

a 49 dB para o caso em que o LNA concentraria todo o ganho do FE.

b Para um ganho de 49 dB, -53 dBm de P1dB pode ser considerado percentualmente equivalente.

Manipulando a Equação (3.14), pode-se definir o fator de ruído esperado do misturador como mostrado na Equação (3.15), onde FMIS é o fator de ruído do misturador,GLNA é o ganho do

LNA,FLNAo fator de ruído do LNA eFFE o fator de ruído do FE.

FMIS=1+GLNA×(FFE−FLNA). (3.15)

Considerando, então, o NF requerido pelo FE de 4,3 dB (Quadro 4), a figura de ruído do LNA de 2,1 dB (Quadro 5), e o ganho do LNA concentrando todo o ganho do FE (49 dB), o NF do misturador pode ser calculado como apresentado na Equação (3.16).

NFMIS≤10 log

1+10

GLNA|dB

10 × 10 NFFE 10 ! −10 NFLNA 10 ! ≤

49,3 dB. (3.16)

Esse valor comprova que, de acordo com a equação de Friis, o NF e o ganho do primeiro bloco de uma cadeia RF tem um impacto maior no NF global do que os seguintes blocos. Logo, para os valores de ganho e NF do LNA utilizados na equação, o misturador pode apresentar até 49,3 dB de NF e ainda assim garantir um NF global de até 4,3 dB.

3.6.2 Ganho

A maior parcela do ganho especificado para oFront-End deve ser fornecida pelo LNA (49 dB). É um notável desafio concentrar o elevado ganho em poucos estágios de amplificação. Busca-se, pelo menos, que nos misturadores não haja perda de conversão de potência, e se possível haja um ganho positivo (em dB), podendo assim relaxar as especificações do LNA.

3.6.3 Linearidade

De maneira semelhante ao que foi feito para extrair o NF do misturador, o seu requi-sito de linearidade pode ser expresso a partir da Equação (3.17)3, considerando os valores de

linearidade esperada para o LNA Quadro 5 e a requerida para o FE (Quadro 4).

IIP3MIS|dBm≥ −30−GLNA|dB−10 log(10(

IIP3LNA|dBm+30

10 )−10(

IIP3FE|dBm+30

10 ))≥-56,0 dBm.

(3.17)

Logo, para os valores de ganho e IIP3 do LNA utilizados acima, o misturador deve ter um IIP3 maior ou igual a -56 dBm a fim de garantir um IIP3 global de pelo menos -72,9 dBm.

3.7 Resumo dos Requisitos do LNA e do Misturador

Baseado nos valores de desempenho típico de um LNA (Quadro 5) e naqueles derivados no decorrer desse capítulo, o Quadro 6 resume os requisitos individuais do LNA e do misturador.

Quadro 6 – Resumo dos Requisitos Iniciais do LNA e do Misturador.

Parâmetros LNA Requisitos Mist. Requisitos

Ganho de Potência(dB) ≥49,0 ≥0,0

Figura de Ruído(dB) ≤2,1 ≤55,4

S11(dB) ≤-21,0 N.D.a

IIP3(dBm) ≥-60,0 ≥-56,0

Consumo(mW) ≤22 N.D.b

4 Topologias

Nesse capítulo, algumas técnicas de projeto de LNA e arquiteturas de misturadores são revisadas. Ao fim de cada seção, topologias que apresentem características condizentes com os requisitos procedentes do Capítulo 3, são escolhidas.

4.1 Amplificador com Baixo Ruído

O amplificador com baixo ruído (LNA) é o um dos componentes mais críticos nodesign

de umFront-End. De acordo com a equação de Friis (ELLINGER, 2007), a figura de ruído de um receptor é primariamente estabelecida pelo seu primeiro estágio de ganho. Por isso, o LNA deve apresentar uma figura de ruído baixa e um ganho considerável.

Para implementar o ganho de 49 dB requerido pelo sistema, utiliza-se um LNA com vários estágios de amplificação. Uma arquitetura do tipo cascode é empregada em todos os estágios a fim de garantir uma boa isolação entre entrada e saída. Para assegurar a figura de ruído mais baixa possível e facilitar o casamento de impedância de entrada, o primeiro estágio do LNA utiliza uma indutância de degeneração e um tanque LC como carga. Para se atingir o restante do ganho necessário, os demais estágios do amplificador de entrada apresentam uma carga resistiva, que fornece um bom ganho com um ruído aceitável.

A seguir, as principais técnicas dedesignde um LNA indutivo são brevemente apresen-tadas e por fim uma topologia é escolhida para servir como referência do primeiro estágio do LNA. Após isso, o segundo estágio é detalhado e seu circuito definido. Finalmente, o conversor de entrada simples para diferencial é determinado.

4.1.1 Técnica CNM -

Classical Noise Matching

Na técnica CNM, o LNA é projetado para exibir a mínima figura de ruído possível, apresentando-se ao amplificador uma impedância de ruído ótima Zopt (HAUS et al., 1960).

Como exposto na Figura 11a, a impedância ótima pode ser alcançada com um circuito de casa-mento de impedância entre a entrada do amplificador (Zin) e a fonte de sinal (Zs). Apesar dessa

técnica permitir alcançar a menor figura de ruído possível, o amplificador verifica ainda uma perda significativa de transferência de potência devido ao descasamento geralmente encontrado entre oZopt e oZin∗ (LEE, 2004).

4.1.2 Técnica SNIM -

Simultaneous Noise and Input Matching

ruído ocorra simultaneamente com o casamento de impedância de entrada, maximizando a transferência da potência e minimizando o NF. Entretanto, essa condição é satisfeita sob o custo de transistores de grande tamanho e alto consumo de energia (BONFIM, 2010).

(a) Técnica CNM (b) Técnica SNIM

Figura 11 – Técnicas de Projeto de LNA

4.1.3 Técnica PCNO -

Power-Constrained Noise Optimization

Uma outra técnica permite que o SNIM seja realizado com um consumo de energia limitado. Foi mostrado em (LEE, 2004) que para uma dada corrente, existe um tamanho de transistor em que o NF do amplificador se aproxima do mínimo. Em outras palavras, é possível otimizar a figura de ruído em circuitos que apresentam uma potência limitada. Para tanto é necessário achar uma polarização que minimize o ruído a uma dada corrente.

4.1.4 LNA Indutivo Escolhido

As técnicas PCNO e SNIM apresentam desempenho de ruído semelhantes, mas con-sumo de energia diferentes. Apesar da PCNO ser mais econômica em potência, a SNIM é mais amplamente utilizada para aplicaçõesnarrowband e é a escolhida para o projeto do LNA cas-codecom degeneração e carga LC. No entanto, várias combinações de polarização serão testa-das até que um compromisso entre consumo e NF seja encontrada.

Dessa forma, a Figura 11b apresenta a topologia de LNA indutivo que mais se ajusta aos requisitos do projeto.

4.1.5 LNA Resistivo Escolhido

sendo que os demais devem assegurar o ganho restante. Esta seção se destina, portanto, a uma breve explanação sobre o LNA com carga puramente resistiva.

Uma topologia de carga resistiva apresenta uma série de desvantagens para a aplicação em questão: comportamentowidebandinerente; redução na excursão de tensão entre a alimen-tação e o dreno do transistor cascode devido ao resistor de carga; inserção de ruído no sinal; e diminuição do ganho. Por outro lado, existem alguns incentivos característicos à utilização dessa carga: aumento da estabilidade do amplificador; aumento da linearidade; simplicidade de

designe menor área ocupada em chip. Além disso, a utilização de resistores em circuitos inte-grados é muito menos problemática que a de indutores, que são componentes maiores e mais complexos (BONFIM, 2010).

Portanto, o LNA de carga resistiva (Figura 12) é escolhido para compor os demais es-tágios do amplificador do FE, graças à sua simplicidade, médio ganho e relativamente baixo consumo e ruído.

Figura 12 – Topologia Escolhida para os Estágios de Ganho do LNA.

4.1.6 Conversor de Entrada Simples para Saída Diferencial

Ainda como parte integrante do LNA, o conversor de entrada simples para saída dife-rencial, ou simplesmente conversor, é discutido a seguir. Poder-se-ia argumentar sobre a real necessidade de se utilizar um conversor desse tipo, mas para simplificar o designe eliminar o uso de um balunexterno (o que adicionaria perda no desempenho) (KO et al., 2005), o LNA é mantido com entrada simples e somente os misturadores apresentam arquitetura diferencial (mais detalhes na Seção 4.2). Logo, há uma necessidade de se converter a entrada simples para uma saída diferencial.

é possível verificar que os ramos positivo (OUT4+) e negativo (OUT4−) são basicamente os

amplificadores resistivos descritos na seção anterior, mas com o capacitor (Cp) promovendo o

acoplamento AC entre eles.

Figura 13 – Conversor de Entrada Simples para Saída Diferencial.

Por último, apesar dessa topologia servir muito bem com um conversor simples para diferencial, ela não suprime não-linearidades de segunda ordem, como circuitos completamente balanceados o fazem (BAGHERI et al., 2006). Isso, contudo, não deve ser um problema, uma vez que essas distorções são mais comuns em receptores de arquitetura Zero-FI.

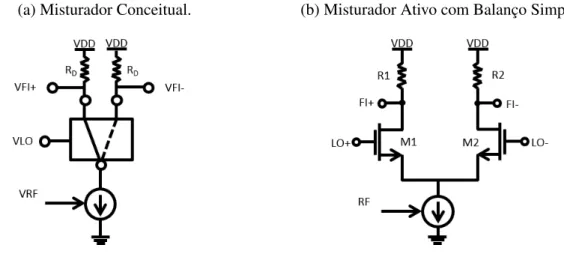

4.2 Misturador

(a) Misturador Conceitual. (b) Misturador Ativo com Balanço Simples.

Figura 14 – Misturadores Conceitual (a) e Simples (b).

4.2.1 Misturador Ativo com Balanço Simples

Aplicando diretamente o conceito apresentado na Figura 14b, realiza-se um misturador utilizando o transistor M1 como estágio de transcondutância e os transistores M2 e M3 como estágio de chaveamento (DESSOUKY; RAGAI; HAFEZ, 2009).

Tal topologia possui uma simplicidade notória, porém exibe o inconveniente da presença do LO diretamente na saída. O filtro passa-baixa que, normalmente, segue o misturador pode não realizar a filtragem adequada do LO sem comprometer o sinal FI (LEE, 2004).

A linearidade do misturador é dominada pelo estágio de transcondutância, e pode ser melhorada por meio de uma degeneração. A adição de um resistor de fonte no transistor M1 oferece uma relação tensão-corrente mais linear, mas gera um perda de ganho e de excursão de tensão, algo crítico em circuitos com baixos níveis de alimentação.

4.2.2 Misturador Ativo Duplamente Balanceado

Figura 15 – Misturador Ativo Duplamente Balanceado.

4.2.3 Misturador Ativo Duplamente Balanceado com Acoplamento AC.

Em aplicações com baixa tensão de alimentação, pode-se desacoplar o nível DC entre o estágio de chaveamento, do estágio de transcondutância, aumentando, dessa forma, a queda de tensão disponível para cada transistor (Figura 16). O projeto dessa topologia é, então, facilitado pelo fato de que a polarização de um estágio não interfere na do outro. Os resistores, R1eR2,

utilizados no estágio de transcondutância oferecem um caminho de alta impedância ao sinal RF, fazendo com que este escolha, ao invés, os capacitores,C1eC2, para fluir em direção aos

transistores de chaveamento (M3aoM6).

4.2.4 Misturador Escolhido

A topologia escolhidado circuito para o misturador é sugerida em (CAMARA, 2012) e mostrada na Figura 17. Trata-se de um misturador ativo duplamento balanceado com aco-plamento DC, também chamado deCurrent Bleeding(LINDBLAD, 2013). O estágio de trans-condutância utiliza a técnica de reuso de corrente, que garante um bom ganho de conversão (KARANICOLAS, 1996). Com essa prática, os resistores, normalmente utilizados no estágio de transcondutância da Célula de Gilbert (Figura 16), são substituídos por transistores PMOS que, além de oferecerem uma alta impedância à corrente AC dos transistores M11 e M12,

re-alizam a amplificação do sinal. Tem-se então uma célula inversora CMOS, composta pelos transistoresM11,M12,P11 eP12, formando a transcondutância (VIDOJKOVIC et al., 2005).

Os resistoresRbias são utilizados na polarização, enquanto oR0 é empregado no

casa-mento resistivo com a saída do LNA. Os transistores M13aoM16 formam o quarteto de

chave-amento. Os resistores RD formam a carga do misturador, que juntamente com o capacitorCD

encarregam-se de uma primeira filtragem do sinal de saída. Os transistoresP13eP14, chamados

decurrent steering, possibilitam a utilização de uma resistência de carga alta sem comprometer a tensão do circuito (ROGERS; PLETT, 2010). Os transistores de chaveamento são polarizados diretamente pela saída do oscilador local, em desenvolvimento por (COSTAJR et al., 2014). E, por fim, dois circuitos seguidor de fonte (transistoresM17eM19) são utilizados comobuffersde

saída do misturador.

4.3 Arquitetura Final do

Front-End

Finalmente, é sugerido umFront-End em quadratura consistindo de um LNA com en-trada simples e saída diferencial, contendo quatro estágios de ganho, e dois misturadores ativos duplamente balanceados com acoplamento DC e com carga RC melhorada porcurrent steering. Um diagrama completo do FE pode ser visto na Figura 18.

A utilização de uma arquitetura com rejeição de imagem (receptor em quadratura), ex-plora a relação entre o sinal desejado e a imagem indesejada para cancelar esta última durante o processo de mistura (LEE, 2004). A saída diferencial do LNA é separada em dois ramos, I

e Q, a partir da utilização de dois conversores simples para diferencial conectados à saída do último LNA resistivo. Essa separação permite isolar os dois misturadores um do outro, evitando degradação devido à sua possível interação (TORMANEN; SJOLAND, 2009).

5 Concepção

Nesse capítulo, é apresentado o procedimento para a concepção do circuito integrado baseado no fluxo de projeto analógico padrão da Figura 19. As topologias apresentadas no Ca-pítulo 4 foram simuladas em nível de transistores até que suas especificações fossem atendidas. Após a obtenção de circuitos funcionais, a etapa delayouté iniciada (Capítulo 6) e os parasitas extraídos. Caso as simulações pós-layoutnão atendem às especificações iniciais do projeto, o fluxo inicia-se até que os requisitos sejam cumpridos.

Nessa etapa do projeto, alguns cálculos iniciais e algumas análises são feitas a fim de se projetar os circuitos. À luz desses valores iniciais, pode-se utilizar o ambiente Virtuoso, da

Cadence Design Systems, em conjunto com o simulador Eldo RF, da Mentor Graphics, para que os parâmetros finais dos circuitos possam ser refinados.

Antes de continuar, vale salientar que odesigna seguir é feito para garantir uma excur-são do sinal na entrada do misturador de 2 mV. Esse valor correspondente ao sinal de maior potência (-99,5 dBm do Quadro 4) amplificado pelo ganho requerido do LNA (49 dB) em uma carga diferencial de 400Ω.

5.1 Amplificador com Baixo Ruído

Inicialmente, para definir as condições necessárias que garantam todos os transistores (NMOS ou PMOS) operando na região de saturação, as Equações 5.1a e 5.1b devem ser satis-feitas.

|VDS| ≥ |VOV|+Vswing, (5.1a)

|VGS| ≥ |VT H|. (5.1b)

OndeVDS é a tensão entre o dreno e a fonte,VOV é a sobre-tensão de condução (VGS

-VT H), VGS é a tensão entre a porta e a fonte,VT H é a tensão de limiar e Vswing é a excursão

máxima do sinal.

5.1.1 LNA com Terminação Indutiva

Figura 20 – LNA Indutivo.

A topologia do LNA com degeneração indutiva e com carga LC, ou simplesmente LNA indutivo, é empregada por apresentar ótimo desempenho de ruído e casamento de impedância de entrada (HUANG et al., 2003). A Figura 20 nomeia todos os componentes utilizados nessa seção.

A polarização do LNA indutivo é feita para assegurar uma distribuição de tensão uni-forme entre os 2 transistores e os indutores de carga e de degeneração. Como a tensão de ali-mentação é de 1,2 V, uma tensãoVDS= 0,5 V representa um bom compromisso para polarizar os

que, consequentemente, aumenta a capacitância entre a porta e a fonte, facilitando assim o ca-samento de impedância de 50Ωpara baixas frequências (401,635 MHz) (BONFIM, 2010). O

valor da sobretensão de condução oferece um compromisso entre ganho e linearidade, ou seja, quanto maior o seu valor, mais espaço para excursão terá o sinal, e portanto maior será a line-aridade do circuito; por outro lado, quanto menor seu valor, maior será sua transcondutância, e assim o ganho aumentará. Dessa forma, as sobretensões de condução são mantidas em 0,2 V para oM1 e 0,3 V para oM2, buscando um compromisso entre linearidade e ganho. As tensões de polarização final e as larguras dos transistores estão resumidas no Quadro 7.

Quadro 7 – Resumo dos Parâmetros do LNA Indutivo.

WM1 209,8µm WM2 70,2µm LM1eLM2 0,18µm VG|M1 485 mV VG|M2 1,2 V

Com os transistores polarizados, o gmM1 e o gmM2 estão definidos e o casamento de

impedância pode ser feito. Na Figura 20 é possível ver que, devido ao seu valor alto de indutân-cia, o indutor de porta (LG) está alocado fora do CI. Isso é necessário, dado a baixa frequência

de operação do circuito. Como mostrado em (HUANG et al., 2003), o LG tem o objetivo de

cancelar a parte imaginária da impedância de entrada, enquanto o indutor de degeneração (LS)

auxilia no casamento da parte real (50Ω). Através de simulações, portanto, é possível anunciar os valores de indutância do Quadro 8 como os capazes de gerar um casamento de impedância de entrada com o parâmetroS11 = -20 dB.

Essa topologia apresenta ainda uma carga em forma de tanque LC, responsável por sintonizar o circuito para trabalhar na frequência desejada (401,635 MHz). De acordo com a Equação (5.2) (ROERMUND; STEYAERT; J., 2003), para assegurar um alto fator de qualidade (Q) e, assim, um alto ganho com um resistência em série pequena, o indutor Lout é escolhido

para ter um valor de indutância próximo do limite da tecnologia (Lout = 25 nH). O requisito

restante de ressonância é atingido, de acordo com a Equação (5.3), pela adição do capacitor

Cout em paralelo com o indutor de carga. Seus valores finais podem ser verificados no Quadro

8.

Q=ω×L/rs (5.2)

Quadro 8 – Resumo dos Componentes Passivos do LNA Indutivo.

LG 198,24 nH

LS 7,21 nH

Lout 25,00 nH

Cout 3,125 pF

5.1.2 LNA com Terminação Resistiva

Figura 21 – LNA Resistivo.

A topologia mais simples de LNA é o de terminação resistiva, ou simplesmente LNA resistivo, como o mostrado na Figura 21. Devido à sua carga resistiva, esse LNA possui intrin-secamente uma banda larga. Mas como esse trabalho precisa ter uma seletividade ao redor de 401,635 MHz, o LNA indutivo se encarrega de sintonizar o circuito para a frequência desejada.

A natureza de sua carga resistiva e a ausência de casamento de impedância de entrada, fazem com que o LNA resistivo apresente naturalmente mais ruído que o indutivo. Isso, con-tudo, não deve ser considerado um problema já que, de acordo com a equação de Friss (LEE, 2004), a figura de ruído total de uma cadeia de blocos RF é principalmente definida pela figura de ruído do primeiro bloco, caso seu ganho seja suficientemente alto.

A polarização do LNA resistivo é feita para assegurar uma distribuição de tensão uni-forme entre os 2 transistores e a carga. Como a tensão de alimentação é de 1,2 V, uma tensãoVDS

= 0,4 V é ajustada para polarizar os transistoresM3 eM4. Para uma corrente de polarização de 2 mA e uma queda de tensão de 0,4 V, o valor da resistência de carga pode ser calculado como 200 Ω. Com o intuito de elevar um pouco o ganho do LNA resistivo, sem, no entanto, alterar

significativamente a sua polarização, o valor de carga é aumentado para 250Ω. As sobretensões

Quadro 9 – Resumo dos Parâmetros do LNA Resistivo.

WM3eWM4 70µm LM3eLM4 0,13µm

VG|M3 350 mV VG|M4 900 mV

RD 250Ω

5.2 Conversor de Entrada Simples para Saída Diferencial

Figura 22 – Conversor de Entrada Simples para Saída Diferencial.

Já mostrado no Capítulo 4, o circuito conversor de entrada simples para saída diferen-cial é redesenhado acima para facilitar sua análise. Os transistores M7,M8,M9 eM10 são uma

réplica do LNA resistivo apresentado na seção anterior e conectados aqui na forma de um am-plificador Pseudo-Diferencial (ROGERS; PLETT, 2010). Ou seja, o ganho fornecido por cada ramo é o mesmo do LNA resistivo, a única peculiaridade nesse circuito é o capacitorCp. Esse

componente permite que o sinal simples que é invertido 180°pelo Amplificador Fonte Comum (AFC) formado pelo M7, seja acoplado para o amplificador fonte comum formado peloM9 e

invertido novamente para 0°. Uma análise mais detalhada pode ser feita considerando a defa-sagem entre os seguintes nós da Figura 22: B e A estão em anti-fase devido ao AFC do ramo

OUT4+, C e B também estão em anti-fase devido ao AFC do ramoOUT4−, D e B estão em fase

e E e C também. Isso comprova, então, que os pontos D e E estão realmente defasados em 180°, sendo o sinal no ponto E com a mesma fase do ponto A.

O balanceamento entre o ramo positivo (OUT4+) e o ramo negativo (OUT4−) do

conver-sor é feito a partir da escolha adequada do valor do capacitorCp. Ou seja, a potência do sinal no

nó C deve ser a mesma do nó B. Para que isso ocorra, o sinal deve ser atenuado pela impedância do capacitorCpo mesmo valor que foi amplificado pelo transistorM7. Dessa forma, através de

Quadro 10 – Valor do Capacitor de Defasamento.

Cp 107,4 fF

O gráfico da Figura 23 mostra uma comparação entre as ondas de saída do conversor de entrada simples para saída diferencial. Em verde está o sinal positivo e em amarelo, defasado em 180°, está o sinal negativo. É visualmente claro o casamento entre os ramos e balanceamento entre as ondas, no entanto, o Quadro 11 exibe com exatidão a diferença entre seus valores de pico-a-pico e de fase, ambos considerados adequados ao projeto.

Figura 23 – Comparação entre o Sinal de Saída Positiva e o de Saída Negativa do Conversor.

Fonte: Retirado do VisualizadorEzwave.

Quadro 11 – Comparação Numérica entre o Sinal de Saída Positiva e o de Saída Negativa do Conversor.

Parâmetros Vo+ Vo−

Tensão de Pico-a-Pico 3,2 mV 3,199 mV

5.3 Misturador

É interessante lembrar que vários fatores podem afetar os parâmetros de desempenho do misturador. Ajustando-se o circuito para tentar otimizar um deles em particular, pode servir para degradar o desempenho de um outro parâmetro. Para que isso seja evitado, um monitoramento constante desses parâmetros é realizado durante todo o processo de concepção.

A Figura 24 subdivide o misturador em vários blocos, que serão projetados individual-mente nas próximas seções. O primeiro deles é o estágio de transcondutância (Seção 5.3.1), que tem como objetivo estimular o estágio de chaveamento (Seção 5.3.2), que, por sua vez, transfere o sinal para o estágio de carga (Seção 5.3.3). Por último, o buffer de saída (Seção 5.3.4), tem como função fornecer o sinal processado peloFront-Endao ADC sem comprometer a desem-penho do misturador. No início de cada subseção, a fim de auxiliar o entendimento, o circuito completo do misturador é repetido com o respectivo sub-circuito destacado.