Rodrigo Adriano Magalhães Azevedo

Implementação de sistemas de encriptação

AES Advanced Encryption Standard em

hardware para segurança

Rodr igo Adr iano Mag alhães Aze vedo outubro de 2013 UMinho | 2013 Im plement ação de sis temas de encr ip tação AES A dv anced Encr yp tion St andar d em har dw ar e para segurança

Universidade do Minho

Escola de Engenharia

outubro de 2013

Tese de Mestrado

Ciclo de Estudos Integrados Conducentes ao Grau de

Mestre em Engenharia Electrónica Industrial e Computadores

Trabalho efetuado sob a orientação do

Professor Doutor João Monteiro

Rodrigo Adriano Magalhães Azevedo

Implementação de sistemas de encriptação

AES Advanced Encryption Standard em

hardware para segurança

Universidade do Minho

Escola de Engenharia

I

Agradecimentos

Em primeiro lugar gostaria de agradecer ao meu orientador, Professor Doutor João Monteiro, pelos valiosos conselhos e pelo apoio dado ao longo do desenvolvimento deste trabalho.

Ao Professor Jorge Cabral pelo conhecimento e interesse partilhado pelo tema, pela ajuda preciosa na análise e abordagem aos problemas e desafios que se apresentaram.

Aos meus amigos e colegas pelos bons momentos, concelhos, discussões e anos académicos.

À minha família por tudo.

III

Resumo

A dissertação aqui apresentada debruça-se sobre o protocolo de encriptação Advanced Encryption Standard (AES), nomeadamente sobre a sua implementação em hardware reconfigurável e sobre a resistência desta a ataques baseados na análise do consumo destes componentes.

O trabalho aqui descrito visa incidir, desse modo, no estudo e implementação de métodos de protecção e countermeasures que permitam estabelecer um nível de segurança contra ataques de Side-channel (SCA) alicerçados na observação e análise de consequências da implementação. Os mais comuns, e os que aqui serão estudados, são os ataques assentes na análise do consumo eléctrico dos componentes, nomeadamente o Single Power Analysis (SPA) e o Differential Power Analysis (DPA). O primeiro é baseado numa observação directa da variação do consumo por parte do atacante que dele retira a informação, identificando-a através do seu traçado. O segundo, bastante mais complexo e eficaz, usa técnicas de correcção de erro e análise estatística para extrair informação, tornando muito mais difícil de prevenir.

Estes ataques baseiam-se no facto de o pico de consumo dos transístores se verificar quando estes transitam de estado. Para um sistema sem nenhuma countermeasure contra este tipo de ataques o consumo energético será directamente relacionado, tanto com o texto a encriptar (plaintext), como com a chave (key) e com o texto cifrado (ciphertext). Munido com o conhecimento dos consumos e do texto encriptado ou a encriptar o atacante, através de métodos de eavesdropping, ou seja escutando o canal de comunicação, pode descobrir parte da chave de encriptação.

É necessário, portanto, dissociar a informação presente aquando do uso encriptador/desencriptador da sua pegada de consumo a qualquer instante do processo. Para este efeito, foram desenvolvidas diversas técnicas, ora baseadas na introdução de factores aleatórios de modo a dificultar o ataque, ora em homogeneizar o consumo ao longo do funcionamento de modo a evitar o dito.

No texto abaixo está descrito o estudo, desenvolvimento, implementação e análise de um encriptador/desencriptador AES em FPGA com as respectivas countermeasures necessárias para poder ser visto como um sistema mais seguro em relação ao tipo de ataques acima referidos.

IV

Abstract

The dissertation presented here debates the Advanced Encryption Standard (AES), namely about its implementation on reconfigurable hardware and its resistance to attacks based on the analysis of the consumption of these devices.

As so, the work here wants to describe the study and implementation of protection methods and countermeasures that allow establishing a security level against Side-Channel Attacks (SCA) based on the observation and analysis of the consequence of the implementation. The ones typically used, the same that are studied here, are attacks based on the analysis of the electrical consumption of the device, namely Single Power Analysis (SPA) and Differential Power Analysis (DPA). The first is based on a direct observation of the variation of the consumption by the attacker that withdraws information from it, identifying it by its trace. The second, a lot more complex and effective, uses technics based on error correction and statistical analysis to extract information, becoming more difficult to prevent.

This attacks are built upon the fact that the peak of the transistor consumption is observed when they change of state. For a system with no countermeasure against these kinds of attacks the energy consumed is directly related with the plaintext, the key and the ciphertext. Equipped with the knowledge of the consumptions and the ciphered or plain text the attacker, using eavesdropping methods, observing a communication channel may discover part of the encryption key.

As a consequence, it is necessary to disconnect the information that is present when the device is in use from its consumption footprint on any instant of the process. To that effect, they were developed several technics, ones based on the introduction of random factors as a way of hindering the attack, others with the intent of normalizing the consumption, during the device work, trying to fully avoid it.

On the text bellow is described the study, development, implementation and analysis to a AES device on FPGA with its countermeasures needed to be seen as a safer system against the attacks designated before.

V

Índice

Agradecimentos ... I Resumo ... III Abstract ... IV Índice de Imagens ... IX Índice de Tabelas ... XI Índice de Fluxogramas ... XIII Glossário ... XVIntrodução... 1

1. Introdução ao protocolo AES e aos conceitos de segurança ... 3

1.1. Advanced Encryption Standard (AES) – Uma nota sobre a sua génese ... 3

1.2. O protocolo ... 5

1.2.1. Expansão da chave ... 6

1.2.2. Adição de Chave da Ronda ... 7

1.2.3. Substituição de bytes ... 8

1.2.4. Troca de linhas ... 9

1.2.5. Mistura de Colunas ... 11

1.2.6. Estrutura das rondas ... 11

1.3. Ataques SCA ... 13

1.3.1. Breve nota sobre diversos tipos de ataques SCA ... 14

1.3.2. Ataques de análise ao traçado de potência ... 17

1.4. Countermeasures contra ataques SCA de análise de consumo ... 17

2. Análise ... 19

2.1. Vantagens e desvantagens do uso de FPGA (Field Programmable Gate Array) em hardware de segurança ... 19

2.2. Análise de ataques SCA de análise de power trace ... 20

VI

2.2.2. Ataques DPA (Differential Power Analysis) ... 23

2.2.3. Ataques High-order DPA ... 24

2.2.4. Ataques de Template ... 25

2.3. Análise de múltiplas countermeasures aplicadas ao AES ... 25

2.3. Análise dos desafios da implementação do demonstrador em hardware ... 31

2.3.1. Análise do sistema ... 32

2.3.2. Comunicação com o demonstrador ... 36

2.3.3. Definição de portos e relógio ... 42

2.3.4. Padding ... 43

3. Implementação ... 47

3.1. Implementação em Software ... 47

3.2. Implementação em Hardware Sem Contramedidas ... 48

3.3. Implementação do Terminal para Computador ... 53

3.3.1. Vectores de teste de funcionalidade ... 53

3.3.2. Vectores de teste de traçado de potência ... 54

3.3.3. Funcionamento regular ... 54

3.4. Implementação em Hardware Usando DRSS ... 57

3.5. Implementação em Hardware Usando n-round ... 65

3.6. Implementação de um protocolo de teste ... 67

4. Análise dos resultados ... 83

5. Conclusão e trabalho futuro ... 91

Bibliografia ... 93

Anexos ... 97

Anexo I – Uso do kit PBS-2 da Aaronia... 99

VII Anexo III - Matlab e C# (Criação de funções e DLL compatíveis com .NET C# usando código Matlab) ... 113

IX

Índice de Imagens

Imagem 1 - Operação Key Expansion ... 6

Imagem 2 - Operação Key Expansion a nivel da palavra ... 7

Imagem 3 - Operação Add Round Key ... 7

Imagem 4 - Operação Sub. Bytes ... 8

Imagem 5 - Operação Shift Row ... 9

Imagem 6 - Operação iShift Row ... 10

Imagem 7 - Polinómio aplicado na operação Mix Columns ... 11

Imagem 8 - Mix Columns ... 11

Imagem 9 - Polinómio aplicado na operação iMix Columns ... 11

Imagem 10 - Representação geral de um ataque SCA ... 13

Imagem 11 - Método de medida para um ataque de análise de potência como proposto por Kocher ... 22

Imagem 12 - SPA Power Trace de uma operação DES completa (in [4]) ... 22

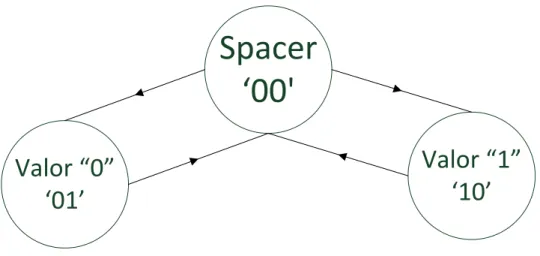

Imagem 13 - Diagrama de Estados DRSS ... 28

Imagem 14 - Diagrama de Estados DRDS ... 29

Imagem 15 - Diagrama de Estados DRDS com valores alternados ... 30

Imagem 16 - Diagrama Duplicated Dual Rail (n-round ) ... 31

Imagem 17 - Diagrama geral do sistema ... 32

Imagem 18 - Placa Virtex XUPV5-LX110T ... 33

Imagem 19 - Diagrama representado a selecção da encriptação/desencriptação ... 34

Imagem 20 - Diagrama da comunicação entre o demonstrador e o terminal ... 37

Imagem 21 - Funcionamento do programa de encriptação desenvolvido em C++... 47

Imagem 22 - Operação de soma (Add Round Key) ... 48

Imagem 23 - Acesso à S-Box... 49

Imagem 24 - Endereçamento S-Box ... 49

Imagem 25 - Operação Shift Row ... 50

Imagem 26 - Multiplicação por 2 ... 51

Imagem 27 - Multiplicação por 3 ... 51

Imagem 28 - Operação Mix Columns para o MSB ... 51

Imagem 29 - Primeiras 3 chaves de ronda (Key Expansion) ... 52

Imagem 30 - Rot. Work (Key Expansion) ... 52

Imagem 31 - Soma da R Con ... 53

Imagem 32- Exemplo de teste de funcionalidade ... 54

Imagem 33 - Funcionamento do terminal durante a encriptação e desencriptação ... 55

Imagem 34 - Erro de encriptação/desencriptação ... 56

Imagem 35 - Erro de padding ... 56

Imagem 36 - XOR DRSS com sinal de Enable ... 58

Imagem 37 - XOR DRSS válido com sinal de Enable ... 59

Imagem 38 - Código Verilog de um XOR DRSS ... 59

Imagem 39 - Esquemática RTL de XOR DRSS ... 60

Imagem 40 - Código Verilog Shift Left DRSS ... 60

Imagem 41 - Funcionamento do conversor S-Box SR/DRSS ... 61

Imagem 42 - Excerto do código da S-Box DRSS gerado pelo conversor ... 62

Imagem 43 - Sub. Bytes DRSS (linhas) ... 63

Imagem 44 - Sub. Bytes DRSS (colunas) ... 63

X

Imagem 46 – Esquemática e top block de conversor DRSS para SR ... 64

Imagem 47 - Traçado 2-round como visto no ChipScope ... 66

Imagem 48 - Traçado 4-round como visto no ChipScope ... 66

Imagem 49 - Traçado 8-round como visto no ChipScope ... 67

Imagem 50 - Montagem para medição ... 68

Imagem 51 - Esquemática regulador 5V para 1V da Xilinx XUPV5- LX110T ... 70

Imagem 52 - Posicionamento da probe ... 70

Imagem 53 - Código de abertura de comunicação VISA (Matlab) ... 71

Imagem 54 - Aquisição de um sinal (canal de trigger)... 71

Imagem 55 - Alinha traçado e calcula variância e média ... 72

Imagem 56 - Rearmar o trigger ... 72

Imagem 57 - Canal do trigger (verde) e do sinal (amarelo) no oscilóscópio... 73

Imagem 58 – Dados alinhados à janela de tempo da encriptação ... 74

Imagem 59 - Função que devolve o estado do osciloscópio ... 74

Imagem 60 - Janela Resultados ... 75

Imagem 61 - Função ataque básico ... 76

Imagem 62 - Ataque básico demonstrador sem contramedidas com 1024 pontos por seed (variância) ... 77

Imagem 63 - Ataque básico demonstrador sem contramedidas com 1024 pontos por seed (média) ... 78

Imagem 64 - Setup com gaiola de Faraday ... 80

Imagem 65 - Teste de funcionalidade do demonstrador sem contramedidas ... 83

Imagem 66 - Ficheiro a ser encriptado para efeitos de teste ... 84

Imagem 67 - Cyphertext do ficheiro encriptado (em hexadecimal) ... 85

Imagem 68 - Ficheiro de teste após a desencriptação ... 86

Imagem 69 - Variância do demonstrador DRSS ... 88

Imagem 70 - Comparação das variâncias dos demonstradores ... 88

Imagem 71 - Variância do demonstrador 8-round ... 89

XI

Índice de Tabelas

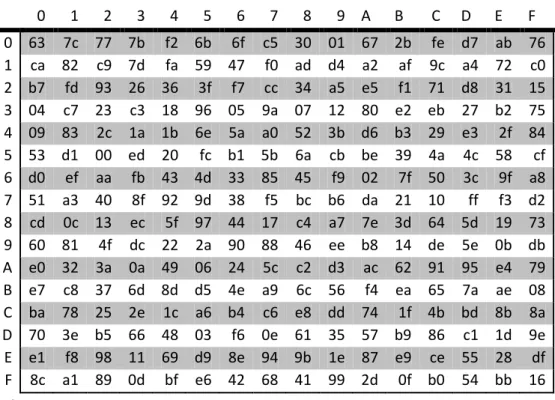

Tabela 1 - S-Box ... 8

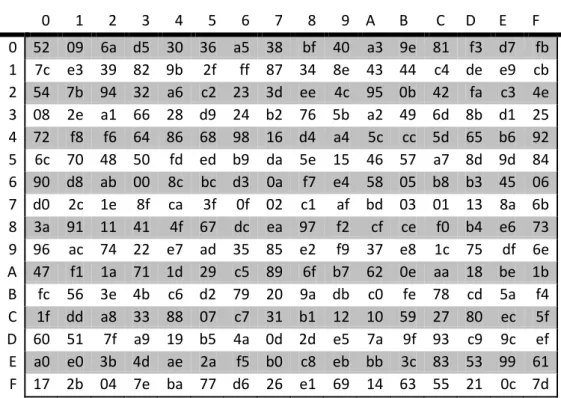

Tabela 2 - Inverse S-Box ... 9

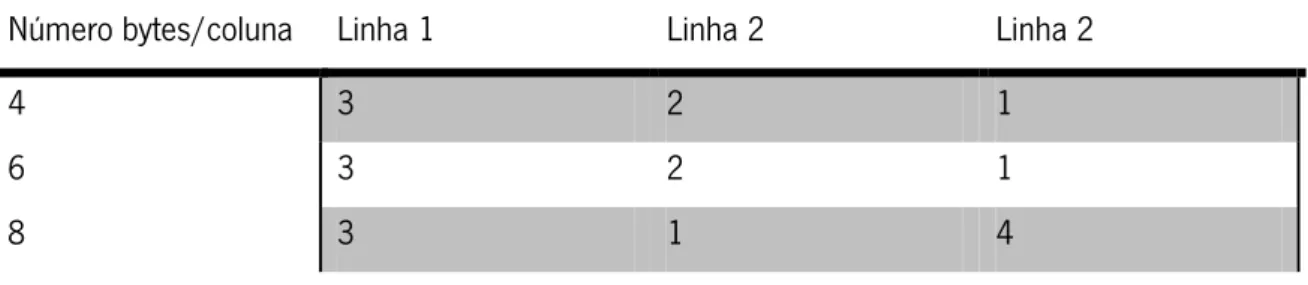

Tabela 3- Rotações executadas na operação Shit Row ... 10

Tabela 4 - Rotações executadas na operação iShit Row ... 10

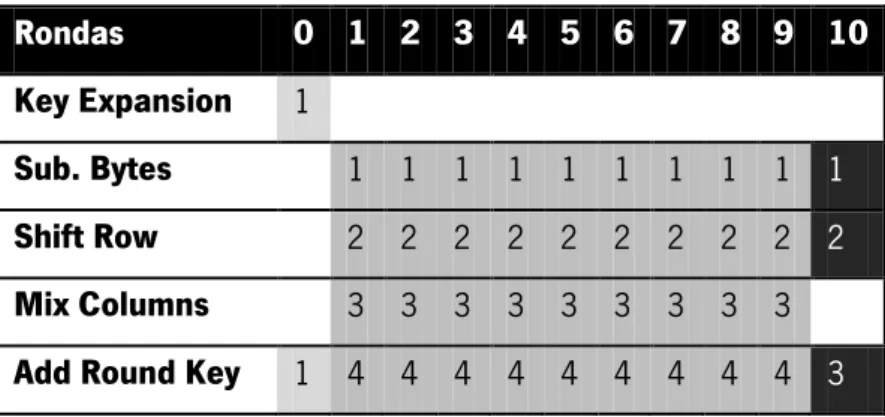

Tabela 5 - Estrutura das Rondas da Encriptação ... 12

Tabela 6 - Estrutura das Rondas da Desencriptação ... 12

Tabela 7 - Codificação Dual Rail Single Spacer ... 28

Tabela 8 - Codificação Dual Rail Dual Spacer ... 28

Tabela 9 - Codificação Dual Rail Dual Spacer Alternado ... 29

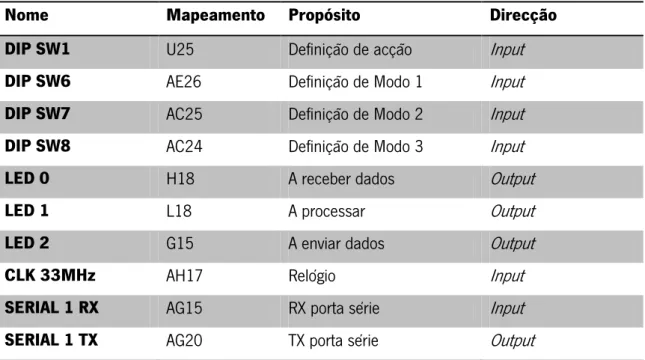

Tabela 10 - Mapeamento na placa ... 43

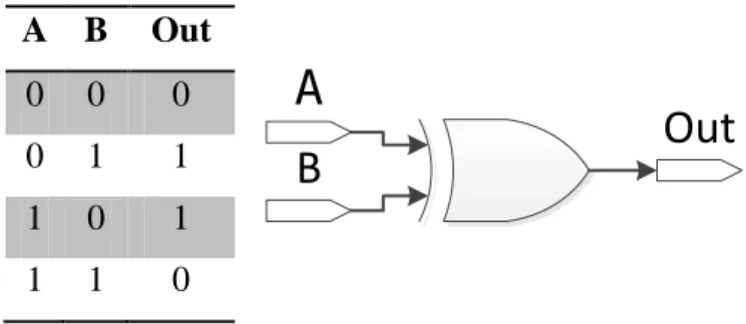

Tabela 11 - Tabela de verdade de um XOR ... 57

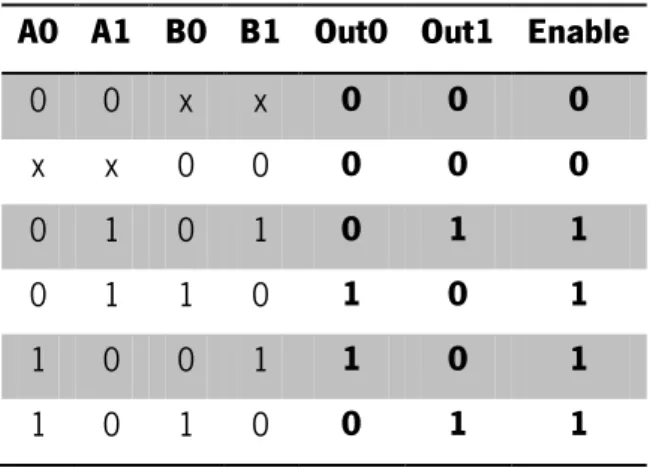

Tabela 12 - Tabela de verdade de um XOR DRSS ... 58

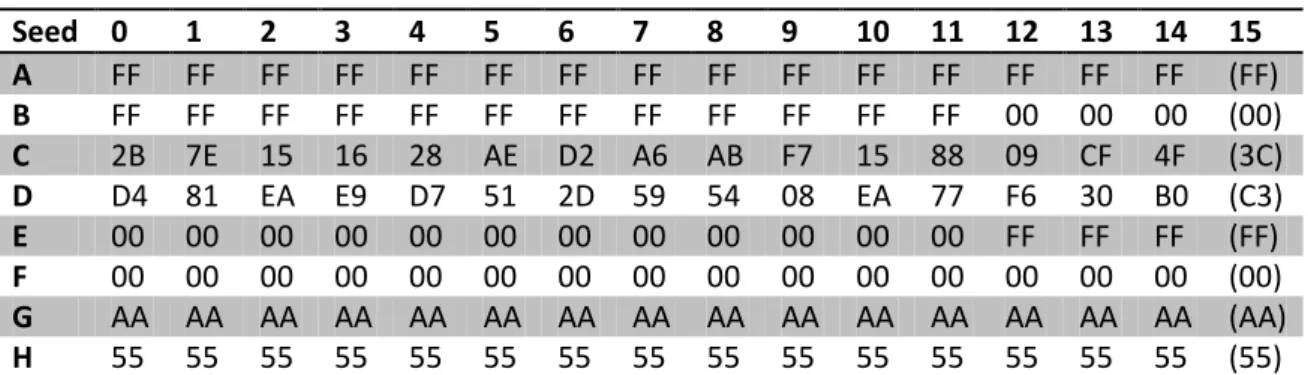

Tabela 13 - Tabela de Seeds ... 77

Tabela 14 - Segunda tabela de seeds ... 87

Tabela 15 - Comparação dos valores das variâncias ... 89

XIII

Índice de Fluxogramas

Fluxograma 1 - Funcionamento geral do demonstrador ... 35

Fluxograma 2 - Funcionamento geral do terminal ... 36

Fluxograma 3 - Funcionamento do terminal durante a encriptação ... 39

Fluxograma 4 - Funcionamento do terminal durante a desencriptação ... 40

Fluxograma 5 - Funcionamento do terminal durante a execução do teste de funcionalidade ... 41

Fluxograma 6 - Funcionamento do terminal durante a execução do teste de traçado de potência ... 42

Fluxograma 7 - Introdução do padding PKCS ... 45

Fluxograma 8 - Remoção do padding PKCS ... 46

XV

Glossário

AES

Advanced Encryption Standard, III, IV, 1, 3, 4, 5, 6, 10, 11, 15, 25, 26, 27, 30, 31, 34, 43, 46, 47, 48, 53, 57, 59, 60, 61, 91, 93, 94

AES128

AES de 128 bits, 6, 9, 10 ASIC

Application-Specific Integrated Circuits, 5, 18, 19, 20, 27, 91, 95 ciphertext

Mensagem encriptada, III, IV, 13, 34, 48 DES

Data Encryption Standard, 4, 22, 93 Diffie-Hellman

Algoritmo de encriptação assimétrica, 15, 93

DLL

Dynamic-link library, 69, 73, 74, 113 DPA

Differential Power Analysis, III, IV, 14, 23, 24, 26, 29, 30, 95 DRDS

Dual Rail Dual Spacer, 29, 30, 65 DRSS

Dual Rail Single Spacer, 27, 28, 29, 57, 58, 59, 60, 61, 62, 63, 64, 65, 87, 88, 89, 90 DSS

Digital Signature Standard, 15, 93 ECB

Modo Electronic Code Book, 34, 46, 48 FEC

Forward error correction, 24 FPGA

Field-programmable gate array, III, IV, 2, 5, 19, 20, 27, 30, 31, 32, 33, 34, 36, 42, 51, 65, 70, 91, 94, 95

High-order DPA

High-order Differential Power Analysis, 24 IDE

Integrated development environment, 47 key

Chave da encriptação, III, IV, 6, 7, 52 MD5

Message-digest algorithm, função de hash criptográfica, 38, 47, 56, 84, 86 PKCS

ou PKCS7, método de padding descrito na norma RFC 5652, 44, 45, 46, 48 plaintext

Mensagem original antes da encriptação ou após a desencriptação, III, IV, 5, 13, 14, 17, 24, 34, 38, 44, 52, 55, 64, 77, 81, 91

RFID

Radio-frequency identification, 23 RSA

XVI

Algoritmo de encriptação assimétrica, 15, 22, 93 SCA

Side-Channel Attacks, III, IV, 13, 14, 17, 20, 21, 25, 27, 37 side-channel

Canal secundário de informação, 19, 21, 25, 26, 68, 91, 92 side-channels

side-channel, 15, 20, 91 SPA

Simple Power Analysis, III, IV, 14, 21, 22, 23 spacer

Valor inválido usado nas codificações Dual Rail, 27, 28, 29, 57, 58, 64

VISA

1

Introdução

A sociedade actual vive suportando-se numa extensa rede de comunicação que usa os mais variados meios. Destes, todos os que dependem da privacidade, desde meios com origens tão remotas, como os o transporte físico de cartas e encomendas, a meios tão sofisticados, como o correio electrónico ou as videochamadas, passando por todos os actuais e futuros, dependem, também, de métodos de segurança para a garantir.

O transporte de informação crítica a longas distâncias é realizado, crescentemente, usando meios de telecomunicações. Qualquer um de nós pode, facilmente, realizar operações financeiras na sua conta bancária, enviar mensagens ou outros dados confidencialmente, e espera que, de facto, as informações transferidas entre o si e o sistema ou pessoa com quem está a contactar se mantenham privadas e seguras. Para esse efeito, com a cada vez maior ubiquidade dos meios electrónicos de comunicação e a velocidade com que estes se mutam e multiplicam, é necessário garantir que, de facto, estes não são vulneráveis a escutas e ataques de terceiros, seja quais forem as suas intenções.

As técnicas de escuta e ataque evoluem em proporção com os fenómenos atrás referidos e, se realmente se deseja manter a confidencialidade de tais mensagens, é necessário manter os métodos de segurança numa constante evolução, garantindo uma resposta satisfatória a novas ameaças, por mais complexas que estas sejam.

Como tal surgiram ao longo dos tempos métodos criptográficos de uma crescente complexidade os quais foram, ora oferecendo segurança, ora sendo derrotados nesse propósito.

O algoritmo criptográfico a ser trabalhado nesta dissertação é conhecido como o protocolo Advanced Encryption Standard (AES). Este protocolo é considerado seguro, sendo, neste momento, inviável executar de forma funcional um ataque que, apenas através de tentativa e erro, usando métodos conhecidos como de força bruta, para descobrir a chave ou o segredo por ele encriptado.

A fraqueza deste sistema reside não na sua base teórica mas sim na implementação prática. Analisando factores inerentes a um processador a realizar a encriptação como o tempo do processo, as falhas ou os consumos energéticos, um atacante pode descobrir informação crítica sobre a chave ou o segredo encriptado.

2

Esta dissertação focar-se-á em estabelecer contramedidas que estabeleçam maior segurança contra ataques baseados nos consumos energéticos, tentando diminuir a vulnerabilidade de um processador dedicado desenvolvido em FPGA.

Para isso tentar-se-á usar técnicas que se baseiam no equilíbrio dos consumos ao longo do processamento do algoritmo evitando a detecção de transições dependentes da chave.

3

1. Introdução ao protocolo AES e aos conceitos de segurança

1.1. Advanced Encryption Standard (AES) – Uma nota sobre a sua génese

Para compreender o tema aqui apresentado é necessário compreender a importância de um conceito mais lato, bem como as suas implicações. Esse conceito, o da segurança nas comunicações, prende-se com implicações de privacidade, bem como de, por exemplo, segurança e idoneidade de operações financeiras ou até de infraestruturas civis ou militares.

Com todos estes pontos críticos em jogo é necessário garantir constantemente a existência de sistemas capazes de oferecer um nível satisfatório de segurança. Um dos garantes mais críticos dessa mesma segurança é a capacidade de transmitir da forma mais inviolável possível a informação entre dois interlocutores, isso é garantido pelo recurso à encriptação.

Os primeiros exemplos conhecidos de métodos de encriptação remontam ao antigo Egipto. Na Grécia Antiga usava-se a cítala, um pequeno bastão no qual se enrolava um cinto no qual se escrevia um texto. Esse cinto era enviado ao destinatário que, ao possuir um bastão igual ao primeiro, lhe era permitido ler a mensagem depois de o enrolar no seu.

Neste método primitivo estavam já presentes os conceitos básicos de todos os sistemas de encriptação: inicialmente o texto não cifrado, ou plaintext, era encriptado com recurso ao sistema de encriptação, ou seja a inscrição do texto no cinto enrolada, e à chave, neste caso a própria cítala, gerando o texto cifrado, ou ciphertext. O receptor da mensagem revertia o processo e recuperava o plaintext, recebendo a mensagem de uma forma segura.

Esses conceitos podem também ser vistos em qualquer sistema de encriptação actual. No caso em estudo, caracterizada por ser um sistema de encriptação simétrico de blocos, usa uma chave conhecida pelos dois interlocutores de modo a permitir a comunicação entre eles, servindo essa chave para realizar acções de encriptar e de desencriptar.

Para compreender os conceitos gerais da criptografia, podemos considerar um exemplo, comum na literatura sobre a mesma, conhecido como Alice, Bob and Eve. Neste exemplo Alice e Bob pretendem comunicar um com o outro através de um meio o qual Eve escuta de forma maliciosa. De forma a esta não conseguir compreende o conteúdo da mensagem, Alice recorre a um método para encriptar com recurso à chave que ela e Bob partilharam num momento prévio.

4

Pode, desse modo, enviar o ciphertext pelo canal de comunicação sem considerações sobre a segurança do mesmo, espectando que a mensagem não seja compreendida por Eve, mas apenas por Bob, que está munido da chave e que é receptor desejado da mensagem.

No entanto estas considerações tradicionais sobre a segurança da encriptação, mantendo-se válidas, estão até certo ponto incompletas, uma vez que se Eve, além de escutar o canal primário de comunicação, escutar, também, a informação cedida pelos processos de encriptação durante a sua execução, pode conseguir informação sobre a chave, podendo até desvendá-la por completo, tornando as precauções tomados por Alice e Bob inúteis.

O trabalho aqui apresentado centra-se na tentativa de evitar que esses mesmos canais secundários, conhecidos como side-channels, cedam informação preponderante sobre a chave, e, desse modo, tornem as comunicações vulneráveis.

Para isso é necessária uma compreensão aprofundada do protocolo de encriptação sobre o qual serão analisadas e implementadas as contramedidas centradas em evitar esse mesmo ataque.

“In January 1997, the US National Institute of Standards and Technology (NIST) announced the start of an initiative to develop a new encryption standard: the AES”. Ao contrário do que se tinha verificado na escolha do protocolo DES (Data Encryption Standard), este concurso seria aberto a todas as propostas que respeitassem os requisitos e a sua avaliação seria feita pela comunidade criptológica.

Embora o espectro deste standard seja pequeno, referindo-se apenas a ser utilizado em documentos ‘sensíveis mas não classificados’ pela administração federal dos EUA, este foi também considerado um certificado da qualidade do protocolo vencedor, sucedendo ao DES que se se tinha tornado o standard de facto da criptografia mundial.

Rijndael foi o vencedor desta competição, passando desde então a ser conhecido como AES. Sendo uma das condições de participação a cifra ser royalty-free, o seu uso rapidamente se expandiu e foi adoptado por diversas outras entidades com uma importância significativa no mundo da comunicação e informação.

5 Os factores mais cruciais na sua escolha foram, para além da sua segurança, a sua performance, custo e a exequibilidade da sua implementação em hardware, quer em FPGA (Field Programmable Gate Arrays), quer em ASIC (Application-Specific Integrated Circuits).

Os ataques de força bruta a esta encriptação são completamente inviáveis uma vez que a menor chave considerada é 128-bits, existindo também 192 e 256, o que significa a existência de 3.4x1038, 6.2x1057 e 1.1x1077, respectivamente, chaves possíveis. Um tão grande número de chaves torna qualquer esforço desse género completamente inexequível uma vez que o tempo necessário de computação seria absurdamente alto.

1.2. O protocolo

O protocolo é, como indicado no concurso do standard, uma cifra de blocos simétrica, ou seja, encripta um bloco de dados de uma dimensão pré-determinada pelos inventores da cifra, neste caso 128 bits. O facto de ser simétrica significa que para desencriptar é necessário inverter os processos matemáticos que tornaram o plaintext em texto cifrado. Para isso a cifra percorre as rondas no sentido contrário usando a inversa matemática de cada uma.

O processo consiste na aplicação de um conjunto de operações matemáticas sobre o plaintext. Essas operações, adição de chave de ronda, substituição de bytes, troca de linhas e mistura de colunas, são executadas de forma sequencial sobre o bloco de dados a ser encriptado, dessa forma encriptando-o.

Para cada ronda existe uma chave expandida da original segundo o algoritmo de expansão, sendo que a mesma é apenas usada durante a adição da chave de ronda.

Ao longo deste capítulo serão expostos em pormenor os processos envolvidos no protocolo AES, o seu funcionamento e a ordenação dos mesmos e das rondas aquando da encriptação e desencriptação.

6

1.2.1. Expansão da chave

O processo de expansão da chave é um ponto essencial na segurança oferecida por este algoritmo de encriptação, no algoritmo AES. No caso do AES128, uma chave com a dimensão de 128 bits, como de resto referido na designação, é, através deste processo, derivada para uma dimensão de 11 vezes o seu tamanho, ou seja 1408 bits usados ao longo das rondas do processo de encriptação.

Com o uso deste processo tentam garantir a segurança face a ataques de related key e a ataques em que parte da chave é conhecida do atacante. De facto, um conhecimento parcial ou aproximado da chave não cede informação suficiente para quebrar o segredo, uma vez que a derivação de duas chaves aproximadas não gerará chaves de ronda, Round Keys, aproximadas.

Olhando para o algoritmo propriamente dito podemos visualizar o seu funcionamento como um conjunto de processos que actuam sobre a chave que inicialmente é dividida em palavras, words, quatro destas no caso do AES128.

De uma forma simplificada esse processo é executado como se pode ver no Imagem 1.

Imagem 1 - Operação Key Expansion

A palavra W(n) é, desse modo, gerada através da execução do algoritmo que consiste na aplicação de um xor, palavra a palavra com a palavra anterior, ou seja W(n-1), e com a palavra

7 W(n-4), ou, sempre que a palavra corresponder a uma palavra em que n seja múltiplo de 4, ao xor de W(n-4) com a aplicação do valor W(n-1) à função g.

A função recorre à rotação da palavra, Rot. Word, rodando a palavra à esquerda uma vez a nível do bit. De seguida, procede à substituição da palavra, Sub. Word, processo análogo à substituição do byte descrita posteriormente, executado a nível dos bytes constituintes da palavra. Finalmente, procede à soma da constante da ronda, RCon. A Imagem 2 representa o seu funcionamento. Wn0 Rot . Wo rd Wn1 Sub. Word Wn1’ ^ RCon W’ Wn1 Wn2 Wn2’ Wn2 Wn3 Wn3’ Wn3 Wn0 Wn0’

Imagem 2 - Operação Key Expansion a nivel da palavra

1.2.2. Adição de Chave da Ronda

A adição de chave de ronda, add round key, é executada através do uso de um “ou exclusivo”, por outras palavras um XOR, entre o estado e a chave da ronda, ou seja através da realização de uma soma entre os dois. A chave da ronda a ser somada é gerada com recurso ao algoritmo de expansão da chave explicada anteriormente.

De uma forma simplificada pode ser vista como representado na Imagem 3. Esta operação é a própria inversa.

A0 A1 A2 A3

KA0 KA1 KA2 KA3

SA0 SA1 SA2 SA3 B0 B1 B2 B3 KB0 KB1 KB2 KB3 SB0 SB1 SB2 SB3 C0 C1 C2 C3 KC0 KC1 KC2 KC3 SC0 SC1 SC2 SC3 D0 D1 D2 D3 KD0 KD1 KD2 KD3 SD0 SD1 SD2 SD3

8

1.2.3. Substituição de bytes

A operação de substituição de bytes, subBytes, consiste numa substituição não-linear, a nível do byte. A tabela de substituição, S-Box, é gerada segundo um conjunto de duas transformações baseadas no campo finito de Galois GF(28).

Tabela 1 - S-Box 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 63 7c 77 7b f2 6b 6f c5 30 01 67 2b fe d7 ab 76 1 ca 82 c9 7d fa 59 47 f0 ad d4 a2 af 9c a4 72 c0 2 b7 fd 93 26 36 3f f7 cc 34 a5 e5 f1 71 d8 31 15 3 04 c7 23 c3 18 96 05 9a 07 12 80 e2 eb 27 b2 75 4 09 83 2c 1a 1b 6e 5a a0 52 3b d6 b3 29 e3 2f 84 5 53 d1 00 ed 20 fc b1 5b 6a cb be 39 4a 4c 58 cf 6 d0 ef aa fb 43 4d 33 85 45 f9 02 7f 50 3c 9f a8 7 51 a3 40 8f 92 9d 38 f5 bc b6 da 21 10 ff f3 d2 8 cd 0c 13 ec 5f 97 44 17 c4 a7 7e 3d 64 5d 19 73 9 60 81 4f dc 22 2a 90 88 46 ee b8 14 de 5e 0b db A e0 32 3a 0a 49 06 24 5c c2 d3 ac 62 91 95 e4 79 B e7 c8 37 6d 8d d5 4e a9 6c 56 f4 ea 65 7a ae 08 C ba 78 25 2e 1c a6 b4 c6 e8 dd 74 1f 4b bd 8b 8a D 70 3e b5 66 48 03 f6 0e 61 35 57 b9 86 c1 1d 9e E e1 f8 98 11 69 d9 8e 94 9b 1e 87 e9 ce 55 28 df F 8c a1 89 0d bf e6 42 68 41 99 2d 0f b0 54 bb 16

A substituição usa o valor do byte a permutar para estabelecer a posição do valor que vai substituí-lo na S-Box.

A S-Box pode ser vista na Tabela 1 e a operação está representada na Imagem 4.

Imagem 4 - Operação Sub. Bytes

A sua inversa consiste numa execução semelhante mas usando o inverso da matriz S-Box, também chama de iS-Box que pode ser vista na Tabela 2.

9

Tabela 2 - Inverse S-Box

0 1 2 3 4 5 6 7 8 9 A B C D E F 0 52 09 6a d5 30 36 a5 38 bf 40 a3 9e 81 f3 d7 fb 1 7c e3 39 82 9b 2f ff 87 34 8e 43 44 c4 de e9 cb 2 54 7b 94 32 a6 c2 23 3d ee 4c 95 0b 42 fa c3 4e 3 08 2e a1 66 28 d9 24 b2 76 5b a2 49 6d 8b d1 25 4 72 f8 f6 64 86 68 98 16 d4 a4 5c cc 5d 65 b6 92 5 6c 70 48 50 fd ed b9 da 5e 15 46 57 a7 8d 9d 84 6 90 d8 ab 00 8c bc d3 0a f7 e4 58 05 b8 b3 45 06 7 d0 2c 1e 8f ca 3f 0f 02 c1 af bd 03 01 13 8a 6b 8 3a 91 11 41 4f 67 dc ea 97 f2 cf ce f0 b4 e6 73 9 96 ac 74 22 e7 ad 35 85 e2 f9 37 e8 1c 75 df 6e A 47 f1 1a 71 1d 29 c5 89 6f b7 62 0e aa 18 be 1b B fc 56 3e 4b c6 d2 79 20 9a db c0 fe 78 cd 5a f4 C 1f dd a8 33 88 07 c7 31 b1 12 10 59 27 80 ec 5f D 60 51 7f a9 19 b5 4a 0d 2d e5 7a 9f 93 c9 9c ef E a0 e0 3b 4d ae 2a f5 b0 c8 eb bb 3c 83 53 99 61 F 17 2b 04 7e ba 77 d6 26 e1 69 14 63 55 21 0c 7d 1.2.4. Troca de linhas

Esta operação, chamada shift row, consiste na troca da posição dos bytes de estado segundo uma tabela fixa. Esta troca é efectuada executando rotações à esquerda com uma dimensão dependente de ambos posição do byte no estado e da dimensão da chave usada.

Uma representação do funcionamento pode ser visto na Imagem 5 para um algoritmo AES128.

10

Esta rotação respeita valores definidos no standard do AES que podem ser consultados na Tabela 3, sendo que a primeira linha da tabela estado nunca sofre rotações.

Tabela 3- Rotações executadas na operação Shit Row

Número bytes/coluna Linha 1 Linha 2 Linha 3

4 1 2 3

6 1 2 3

8 1 3 4

Para executar a desencriptação é preciso proceder à sua inversa, para isso é necessário executar as rotações de modo a serem colocados os bytes na posição inicial, ou seja, as rotações a tabela das rotações da operação inversa passa a ser a patente na Tabela 4.

Tabela 4 - Rotações executadas na operação iShit Row

Número bytes/coluna Linha 1 Linha 2 Linha 2

4 3 2 1

6 3 2 1

8 3 1 4

O que se reflecte para um AES128 numa operação semelhante à representada na Imagem 6.

11

1.2.5. Mistura de Colunas

Esta operação consiste na multiplicação de cada valor da matriz de estado por um polinómio, alterando efectivamente os valores da primeira e “misturando” as colunas. Esse polinómio pode ser visto na Imagem 7.

( )

Imagem 7 - Polinómio aplicado na operação Mix Columns

Desta multiplicação pelo polinómio resulta uma operação semelhante à visível no Imagem 8. SA0 02 03 01 01 A0 SB0 01 02 03 01 B0 SC0 01 01 02 03 C0 SD0 03 01 01 02 D0

Imagem 8 - Mix Columns

Para desencriptar é necessário executar o polinómio inverso, que pode ser visto na Imagem 9.

( )

Imagem 9 - Polinómio aplicado na operação iMix Columns

1.2.6. Estrutura das rondas

O funcionamento do AES é constituído por diversas fases, designadas rondas, como já atrás referido. Estas correspondem ao conjunto das operações executadas sobre os dados nele introduzido.

Essa estrutura, descrita aqui no caso do AES-128, é constituída por um conjunto de 10 rondas, bem como um conjunto de operações que precedem a primeira dessas.

A chave introduzida pelo utilizador é apenas usada directamente em duas fases da encriptação, nomeadamente na expansão da chave e durante a primeira adição de chave de ronda. Ambas as operações são realizadas precedendo a primeira das rondas.

12

À excepção da última ronda, todas são constituídas pelas 4 operações descritas na seguinte sequência:

Sub. Bytes;

Shift Row;

Mix Columns;

Add Round Key.

Na última ronda a operação Mix Columns é omitida, sendo esta ronda constituída apenas pelas outras 3 operações seguidas na mesma ordem. Na Tabela 5 podemos visualizar esquematicamente o conjunto das rondas na encriptação.

Tabela 5 - Estrutura das Rondas da Encriptação

Rondas 0 1 2 3 4 5 6 7 8 9 10 Key Expansion 1

Sub. Bytes 1 1 1 1 1 1 1 1 1 1 Shift Row 2 2 2 2 2 2 2 2 2 2 Mix Columns 3 3 3 3 3 3 3 3 3

Add Round Key 1 4 4 4 4 4 4 4 4 4 3

1.2.6.1. Estrutura da desencriptação

A sequência de desencriptação funciona aplicando de uma forma simétrica as inversas de cada uma das operações aplicadas, como poder ser visto na Tabela 6.

Tabela 6 - Estrutura das Rondas da Desencriptação

Rondas 0 1 2 3 4 5 6 7 8 9 10 Key Expansion 1

Add Round Key 1 1 1 1 1 1 1 1 1 1 1 iMix Columns 2 2 2 2 2 2 2 2 2

iShift Row 2 3 3 3 3 3 3 3 3 3

13 Todas as rondas excepto a final consistem nas 4 operações inversas às da encriptação, sendo a Add Round Key a sua própria inversa, executadas segundo a ordem:

Add Round Key;

iMix Columns;

iShift Row;

iSub. Bytes.

1.3. Ataques SCA

Na criptografia clássica assumia-se a função de encriptação como uma caixa negra, sobre a qual o atacante não obteria qualquer tipo de informação interna, apenas o plaintext e o cyphertext. Ao analisar implementações de algoritmos de encriptação, observa-se que, na realidade, tal não se verifica. Na verdade, ao executar uma função de encriptação, um sistema, seja ele de software ou de hardware, cede uma miríade de informações ao exterior, assemelhando-se a uma situação como a representada na Imagem 10.

Emissor

Receptor

Atacante Consumo energético Som Radiação electromagnética Tempo Falhas Luz Consumo energético Som Radiação electromagnética Tempo Falhas LuzImagem 10 - Representação geral de um ataque SCA

Os ataques Side-channel (SCA) apoiam-se neste facto, explorando pelo menos um dos canais de informação cedido ao exterior pela função encriptadora em conjunto com o plaintext ou o ciphertext.

14

Desse modo, para executar um ataque deste género, um adversário A tem que assumir, como descrito em [2], dois conceitos:

“Assumption 1 (Kerckhoffs’ extended principle) A knows all technical details about the underlying cryptographic algorithm and its implementation. (…)

Assumption 2 A is able to get plaintexts (or ciphertexts) of encryptions. Furthermore, foreach encryption A is able to obtain side channel information“1

Estes ataques assumem duas fases distintas: numa examinam a implementação que desejam atacar; noutra tentam relacionar as medições obtidas com estádios intermédios da encriptação.

O objectivo central deste ataque é permitir que o atacante conclua algo sobre a natureza da chave e, desse modo, desvendar os segredos transmitidos nesse canal, usando a chave para revelar a natureza do plaintext.

O primeiro ataque deste SCA a ser realizado com sucesso foi um ataque de timing descrito em [3] por Kocher em 1996. O seu trabalho focou-se em medir cuidadosamente os tempos de processamento das múltiplas cifras que analisou usando-os para obter informação sobre a chave.

Em 1998, estendendo o conceito de SCA, foi proposto o primeiro ataque funcional baseado na análise do tratado de consumo em [4] por Kocher et al. Nesta proposta são descritos ambos, SPA e DPA, e são discutidos alguns conceitos sobre como os evitar.

Nos pontos que se seguem serão descritos de uma forma não pormenorizada múltiplos tipos de ataque SCA, para depois incidir a descrição de forma pormenorizada nos ataques de análise de traçado de potência e contramedidas desenvolvidas de forma a contraria-los.

1.3.1. Breve nota sobre diversos tipos de ataques SCA

Aqui serão brevemente expostos, a título informativo, alguns conceitos sobre múltiplos géneros de ataques SCA, nos quais esta dissertação não se focará. Faz portanto sentido analisar

1in [2] pag. 20-21

15 primeiramente os ataques de timing como precedentes, evoluindo daí para a referência de outros ataques de interesse.

O primeiro ataque com sucesso, recorrendo à análise de timing, foi, como atrás referido, descrito pela primeira vez em [3] usando-o para atacar múltiplas cifras, nomeadamente RSA, Diffie-Hellman e DSS.

Este tipo de ataques concentra-se em correlacionar a duração variável do processo de encriptação com a chave usada no mesmo. Kocher descreve-o como um ataque que pode ser alterado de modo a ser eficiente contra qualquer cifra cuja implementação tenha uma duração variável.

O conceito de ataque de timing foi posteriormente trabalhado e, como tal, aperfeiçoado, como por exemplo em [5], e adaptado a cifras simétricas acabando por ser finalmente aplicado ao AES em [6]. Aqui, considerando uma aplicação descuidada da cifra, na fase da Mistura de Colunas, da qual se poderia obter uma variação temporal mensurável, através da qual seria possível obter uma chave, com grande probabilidade de ser a certa, recorrendo a um método de baixo custo.

O relatório técnico atrás referido foi realizado ainda durante a fase de escolha da cifra que viria a ser conhecida por AES. No entanto os autores do mesmo sublinham que a descoberta desta vulnerabilidade em aplicações mais descuidadas não deveria ser tida em conta face a essa mesma escolha, uma vez que a implementação desenvolvida pelos criadores da cifra Rijndael, actualmente mais conhecida por AES, num microprocessador 8051 não mostrava nenhuma vulnerabilidade a este método. Frisam, no entanto, a necessidade de o standard que estava à escolha ser implementado de modo pensado.

Esforços baseados no conceito do ataque de timing continuaram a ser desenvolvidos, tendo sido desenvolvido o mesmo ao ponto de ser capaz de recuperar a chave de uma cifra RSA de um servidor recorrendo ao uso e interpretação de medições de tempo numa rede como exemplificado em [7] e em [8].

Um método de ataque também baseado no conceito da observação de side-channels é o ataque de falhas, em inglês fault attack. Este tipo de ataque baseia-se na indução de falhas em

16

circuitos criptográficos de modo a que estes cedam informação sobre a chave. Esta técnica foi pela primeira vez introduzido em [9].

Os ataques deste género podem recorrer a diversos métodos para criar falhas, usando picos na energia fornecida ao circuito, alterações do relógio do sistema, indução de erros com recurso a diversos tipos de radiação (raios X, feixes de fotões e luz visível), correntes parasitas ou até temperatura.

A maneira de examinar as falhas causadas pode basear-se na análise do número de bits afectados, a forma como o processador criptográfico reage ao erro e, até, a propagação do mesmo no processo, bem como na observação do output erróneo do sistema, ou até a ausência do mesmo.

Dito isto estes ataques podem revelar-se bastante eficientes sendo necessário, nomeadamente para aplicações como smartcards cuja alimentação e relógio são fornecidos externamente, algum cuidado para os evitar.

Existe ainda uma miríade de ataques aproveitando diferentes comportamentos adoptados para melhorar o throughput, nomeadamente o recurso a memórias de cache, tendo o primeiro ataque sido proposto sobre a sua forma teórica em [10].

Comprovando a necessidade de constante evolução das contramedidas são divulgados, de forma contínua pela comunidade académica, novos métodos de ataque, como é o exemplo do artigo recentemente divulgado pelo MIT, em [11], conjugando o desgaste dos escudos desenvolvidos para tornar os componentes de segurança invulneráveis a alguns dos ataques descritos neste ponto, e, desse modo, usar uma observação directa das operações com recurso a microscópio laser incorporado com uma câmara infravermelha, permitindo a leitura directa da emissão de calor do componente executando a operação criptográfica e, assim, descobrir a chave.

Embora ataques como o atrás referido sejam provas de conceito e dificilmente executáveis em situações reais, devido ao custo de implementação, eles comprovam a evolução dos método invasivos, podendo tornar-se rapidamente um risco para a segurança da encriptação.

17

1.3.2. Ataques de análise ao traçado de potência

Uma das famílias mais comuns e eficientes, de entre os ataques SCA, diz respeito a ataques baseados na análise do consumo energético de um componente a executar uma encriptação. Estes analisam a variação ou o traçado do consumo, conhecido por power trace, ou traçado de potência, recorrendo a múltiplas ferramentas, desde simples observação a olho nu a complexas análises matemáticas, de modo a tirar conclusões sobre a informação que está a ser processada pelo dispositivo em análise, seja ela referente à chave ou ao plaintext.

Uma vez que o principal foco desta dissertação é a prevenção desta família de ataques, esta será analisada de uma forma mais prolongada no capítulo 2, bem como os factores que permitem o uso deste ataque contra as implementações em hardware.

1.4.

Countermeasures

contra ataques SCA de análise de consumoOs ataques de análise de consumo baseiam-se na análise dos picos de consumo dos transístores. Esse pico de consumo traduz uma transição de estádo, ou seja, uma transição entre 0 e 1 ou vice-versa.

De modo a evitar este tipo de ataques é necessário fazer com que o consumo deixe de ser consequência da chave. Para isso foram desenvolvidas diversas técnicas, umas, introduzindo uma máscara gerada de forma aleatória, que visam dificultar o ataque com ela; outras visam homogeneizar o consumo ao longo do funcionamento, tentando torna-lo realmente independente do que este processa.

Neste ponto serão introduzidos dois conceitos de forma breve, sendo as consequências da sua aplicação e os seus métodos de implementação discutidos em mais profundidade no ponto 2.3.

Comece-se por referir os métodos de randomizing, que se centram na tentativa de esconder a visibilidade do processamento da informação de interesse, neste caso a chave, no traçado de consumo. Para isso foi proposta uma família de soluções que considerava efectuar alterações a nível do algoritmo. Estas propõem o acrescento e remoção de uma máscara gerada

18

aleatoriamente durante a execução das rondas, pretendendo com isto acrescentar variações que alterem e escondam o impacto do algoritmo sem contramedidas no traçado de consumo.

Este tipo de contramedida foi pela primeira vez proposta em [12] por Messerges, e foi evoluindo com diversos conceitos, sendo consideradas por exemplo em [13], [14].

O outro conceito que foi largamente explorado foi o método do balanceamento do traçado de potência que, ao invés do descrito anteriormente que pretende esconder, intenta evitar que este detenha informação relevante, tentando que este seja constante.

Para isso considera diversas técnicas, tentando procurar que durante o processo de encriptação ocorra sempre o mesmo consumo através do recurso a alterações a nível da implementação, e não do algoritmo como o primeiro.

Devido a isso uma técnica funcional que seja desenvolvida para estes métodos para qualquer algoritmo criptográfico pode ser aplicada a outros, sobre a implementação destas técnicas em ASIC como pode ser lido o artigo [15].

19

2. Análise

Neste capítulo serão primeiramente analisadas as vantagens e desvantagens do uso da tecnologia FPGA na implementação de hardware de segurança. Posteriormente será estudada a exploração das vulnerabilidades face à exposição do side-channel que representa a variação do consumo e, finalmente, examinadas as contramedidas propostas para sanar esse mesmo canal de informação secundária.

2.1. Vantagens e desvantagens do uso de FPGA (Field Programmable Gate Array) em hardware de segurança

A tecnologia FPGA é uma alternativa poderosa para criar aplicações de sistemas embebidos. Devido às suas características, que combinam algumas das vantagens do software e do hardware, esta tecnologia oferece características únicas que fazem com que seja um candidato ideal para muitas aplicações, nomeadamente, considerando o âmbito desta dissertação, a nível das aplicações de segurança.

O facto de ser hardware reconfigurável permite que uma FPGA atinja throughput bastante alto, superior, por exemplo, ao de um sistema embebido desenvolvido em software funcionando sobre um microprocessador, mas inferior às velocidades obtidas por um sistema implementado em ASIC.

Permite também que o sistema depois de desenvolvido seja facilmente actualizado ou reconfigurado permitindo facilmente acrescentar funções, alterar o algoritmo implementando, corrigir bugs, entre outras funções, sem custo acrescentado, algo que os ASIC não permitem.

Como consequência do atrás referido, tem inúmeras vantagens a nível do time-to-market em relação aos processadores dedicados ASIC uma vez que permite o teste em fases iniciais do desenvolvimento, possibilitando um tempo mais reduzido de testes, tendo como consequência que executar o desenvolvimento e o deployment nesta tecnologia é mais eficiente em termos de custos do que o desenvolvimento da mesma em ASIC.

20

No entanto é necessário considerar que, de resto como todas as tecnologias, usar FPGA pode trazer vulnerabilidades e desvantagens.

Devido a ser reprogramável, a FPGA pode ser alvo de ataques como a clonagem, injecção de código malicioso, alterações ao hardware programado de forma a cumprirem funções indesejadas, como de resto discutido em [16] [17], engenharia reversa através da recolha do bitstream desencriptado ou desencriptação do mesmo, como feito em [18]. Estas vulnerabilidades podem levar a contrafacções ou ataques que comprometam a integridade do sistema ou permitam a recolha de informação por parte de terceiros, pode ainda expor vulnerabilidades da implementação cuja exploração a tornam insegura ou nefasta.

Além disso, a aplicação de sistemas de segurança em FPGA levanta também múltiplos problemas face a vulnerabilidades advindas da forma como a tecnologia em causa funciona, nomeadamente a nível do balanço do consumo de energia.

Devido ao modo como o design flow das FPGA foi desenhado, facilitando o seu uso, a implementação ou aproximação de técnicas usadas em ASIC, para os proteger de ataques SCA, demonstram-se difíceis ou, pelo menos, pouco práticas, sendo necessário para isso alterar manualmente alguns parâmetros gerados pelas ferramentas fornecidas pela FPGA, como realizado em [19] que demonstra uma alteração ao design flow para implementar alguns conceitos já comprovados em ASIC.

No entanto existem propostas alternativas a uma alteração tão profunda como a proposta em [19], desenhadas de modo a evitar expor side-channels a terceiros. Essas propostas serão analisadas no ponto 2.3 e os ataques baseados na análise da informação cedida pelo consumo no ponto 2.2.

2.2. Análise de ataques SCA de análise de

power trace

O conceito por detrás desta família de ataques SCA foi primeiro descrito em [4], e para ser entendido é necessário relembrar a forma como os transístores constituintes da lógica digital funcionam.

21 Um transístor usado em lógica digital funciona essencialmente como um interruptor, ora permitindo ora bloqueando a passagem da corrente através dele. Durante o seu funcionamento, e sempre que num destes estados, o consumo de um transístor é mínimo. No entanto, sempre que este transita de estado existe uma perda de comutação que representa uma visível e momentânea alteração no consumo do mesmo.

É na recolha dessa variação de consumo com side-channel que esta família de ataques se baseia para obter informação. Analisando os traçados de potência é proposto obter através de variados métodos de observação, descritos mais abaixo, a chave usada na encriptação.

Este tipo de ataques pode ser adaptado para funcionar com variados algoritmos de encriptação através do conhecimento aprofundado do seu funcionamento, alterando o modo como se analisa os valores obtidos.

No entanto este ataque, como de resto os ataques SCA em geral, foca-se nas vulnerabilidades a nível da implementação, e é esta que permite a sua existência cedendo, de uma forma ou de outra, algum tipo de side-channel, neste caso a variação do consumo de um processador ou co-processador.

2.2.1. Ataques SPA (Simple Power Analysis)

Este tipo de ataques é baseado numa observação directa da variação do consumo por parte do atacante, sendo considerado o menos ameaçador uma vez que a sua prevenção é notavelmente mais fácil que a dos restantes ataques descritos neste ponto.

Para executar este método o adversário recolhe um power trace, ou seja, através de um número de amostras recolhidas durante a execução de uma encriptação é realizado um gráfico que permite visualizar a esses mesmos pontos. Um osciloscópio em modo de disparo pode ajudar a realizar este trabalho se o segundo passo for realizado directamente pelo adversário humano.

Em [4], Kocher et al, propõe, para a recolha das variações do consumo o uso de uma resistência pequena, por exemplo 50Ω, em série com a alimentação ou massa do componente em análise, como pode ser visto na Imagem 11. Medindo a queda nesta resistência é facilmente

22

calculada a variação de corrente e, consequentemente, do consumo do dispositivo em observação.

Imagem 11 - Método de medida para um ataque de análise de potência como proposto por Kocher

Analisando a informação assim recolhida é possível descobrir informações sobre o funcionamento do dispositivo em análise bem como da chave em uso. Para descobrir tais informações este método recorre então à análise do power trace.

Esta análise pode ou não ser automatizada, sendo possível a um atacante humano munido desta informação realiza-la facilmente. Na Imagem 12 pode visualizar-se um traçado obtido por esta técnica.

Imagem 12 - SPA Power Trace de uma operação DES completa (in [4])

Fazendo uma análise mais pormenorizada, com uma escala temporal e de corrente mais alta alguns dos valores são visíveis podendo concluir o valor de alguns bits.

Este género de ataque é bastante eficiente contra a cifra DES, permitindo visualizar o processamento dos dados da execução, podendo também ser usado na cifra RSA, contra as suas operações de multiplicação. No entanto as técnicas de protecção contra esta análise são de fácil implementação.

VCC GND

23 Um modo alternativo de recolha deste tipo de informação é proposto e extensivamente discutido por Kasper et al [20]–[22] recorrendo ao uso e recolha da radiação electromagnética produzida pelo funcionamento de smartcards lendo RFID de modo a encontrar chaves de encriptação.

No caso prático descrito por Kasper a exploração destas ondas electromagnéticas, para o efeito de ataque à encriptação, a recolha do traçado seria feita por uma near-field probe colocada de modo a interceptar a comunicação entre a smartcard e um cartão RFID. Face à intercepção desta seria necessário desmodular a onda e sincronizá-la de modo a permitir retirar conclusões sobre o conteúdo da chave.

A necessidade desta desmodulação parte do facto de a amplitude das ondas rádio ser modulada por consequência das necessidades energéticas do chip incluído no RFID, ou seja, por exemplo quando este necessitar de maior energia existe uma diminuição da amplitude destas. Como consequência desta desmodulação foi conseguido o esperado traçado do consumo, permitindo aplicar os algoritmos desenvolvidos para executar a análise sobre este.

Através desta técnica Kasper et al conseguiram realizar um ataque com bastante sucesso a um módulo black box, permitindo-lhe retirar bastante conclusões sobre ele e a sua chave.

2.2.2. Ataques DPA (Differential Power Analysis)

Os ataques desta natureza baseiam-se também, tal como a SPA, na recolha e análise do power trace, no entanto as semelhanças não se prolongam muito para além desse ponto. Ao invés da observação directa que caracteriza o SPA, no DPA são usadas extensivamente ferramentas estatísticas e de correcção de erros para tirar conclusões sobre a natureza da chave.

O ataque pode ser visto como o conjunto de duas fases, tal como descrito por Kocher et al em [4], uma fase de recolha e uma fase análise.

A fase de recolha é, de uma forma básica, semelhante à da descrita para o SPA, podendo ser baseada no mesmo tipo de montagem de hardware para proceder à recolha de informação sobre a potência consumida ao longo do tempo. Quanto mais extensa esta fase

24

maior será número de amostras recolhidas sobre o dispositivo sob ataque e, como tal, mais eficiente a aplicação do mesmo.

Para ser possível obter dados desta implementação é necessário recolher uma quantidade de dados relativamente alta, permitindo desse modo uma análise estatística relevante dos dados. Munidos com estes valores procedesse ao recurso de análise com base em diversas ferramentas matemáticas, como a variância, a média, ou até a correlação, examina-se a informação presente no traçado.

Recorrendo a esta análise espera-se detectar um comportamento conhecido e relacionado com a proximidade do valor do plaintext em relação ao valor da chave. Usando esse comportamento para executar a aproximação à chave é possível descobrir parte, ou a totalidade, da mesma.

A diferença entre a análise usada para realizar o DPA e a análise descrita atrás para o SPA é que um atacante, usando este último, se centra na análise simples, directa e visual de um traçado de consumo, sem recurso a mais ferramentas que essa mesma observação. No primeiro ataque, por sua vez, o executor centra-se na análise de valores obtidos a partir da análise matemática de múltiplos traçados, permitindo uma análise muito mais eficiente de informação recolhida, e, como tal, sendo bastante mais complexa de evitar.

2.2.3. Ataques High-order DPA

Os ataques do tipo High-order DPA concentram-se na recolha de um maior número de amostras e no uso de algoritmos de FEC e filtragem mais poderosos e avançados que os usados num tradicional ataque DPA.

Os métodos de recolha dos dados e execução do ataque são em tudo semelhantes ao anteriormente descritos. A grande diferença entre este método e a DPA normal é o número de traçados recolhidos, muito maior na técnica em discussão, e a complexidade da análise matemática executada, usando este método uma sofisticação muito superior para examinar as amostras, o que o torna mais eficaz.

25

2.2.4. Ataques de Template

Os ataques de Template, tal como o descrito em [23] (neste já dedicado a cifras de bloco), e primeiro introduzido como conceito em [24], usam métodos, também baseados na interpretação de amostras recolhidas do side-channel, diferentes dos anteriores para obter a chave.

Embora a primeira descrição deste método não refira exclusivamente o uso de traçado de consumo de modo a obter as chaves usadas nos métodos analisados como prova de conceito, a sua aplicação à AES, em [23], descreve o uso desse mesmo side-channel para obter informações da chave. Como tal considerou-se relevante a sua referência neste ponto.

O pressuposto base desta técnica é que o atacante possua um aparelho idêntico ao sob escuta e possa introduzir e controlar de forma arbitrária o mesmo. Cumprindo esta suposição o atacante pode começar a estabelecer o seu ataque de Template, ou seja, a por em prática uma das mais poderosas de SCA.

O ataque é dividido em duas fases, uma, conhecida por profiling, cria um perfil do encriptador, o template que dá o nome ao ataque, usando um grande número de amostras enquanto o dispositivo sobre ataque executa o algoritmo de encriptação. A segunda fase, classification, compara os valores recolhidos com um template particular usando uma distribuição Gaussiana multivariável para calcular a probabilidade. Os valores correctos terão uma probabilidade muito superior aos dos incorrectos sendo assim obtida a chave.

Este tipo de ataques é ainda mais poderoso pois a sua fase mais prolongada e intensiva é a fase de construção dos templates. Esta fase, no entanto, só necessita de ser usada uma vez por cada conjunto de encriptadores idênticos, podendo, após obter o template de um usa-lo para atacar todo e qualquer componente semelhante.

2.3. Análise de múltiplas

countermeasures

aplicadas ao AESAs vulnerabilidades atrás descritas levaram a comunidade a pesquisar métodos para evitarem a exposição de informação através do side-channel. Esses esforços foram desenvolvidos em dois sentidos diferentes, um no de tentar tornar aleatória a informação oferecida pela fuga de

26

informação, o outro foi no de tentar equalizar a saída de forma a que esta não cedesse qualquer tipo de informação.

A opção pelo método baseado em tornar aleatória a informação cedida pelo side-channel exige a alteração do fluxo de execução do algoritmo, acrescentando e retirando valores aleatórios ao longo do processo de encriptação ou de desencriptação.

Estes processos são extensivamente discutidos e descritos em artigos como [25], [13], [14], [26], oferecendo distintas abordagens ao método conhecido como masking. Este método exige uma aplicação dedicada ao algoritmo e pode gerar algumas vulnerabilidades com a sua implementação, nomeadamente a chamada zero-value fault que é conhecida e bastante explorada em vários artigos.

De uma forma bastante simplista, os artigos referem-se à alteração do algoritmo AES de modo a permitir a inclusão de uma máscara aleatória com a qual será executada uma operação matemática com alguns dos estados, sendo posteriormente feita operação em ordem à sua remoção.

Da natureza destas contramedidas resulta o facto de estarem vulneráveis até certo ponto a ataques DPA mais desenvolvidos, oferecendo algumas vulnerabilidades acrescidas como o zero-value fault atrás referido. Em [27] é demonstrado um ataque eficiente contra alguma da concepções por detrás desta contramedida.

Por oposição e como atrás referido com a intenção de obter a equalização do traçado de consumo, independentemente da existência, ou não, de transições, procurou-se encontrar um método de implementação cujo referido traçado não revelasse qualquer relação com as mesmas e, como tal, com a chave. Com esta pretensa foi pensada a implementação do Dual Rail nos circuitos encriptadores.

Os circuitos implementados sobre este conceito usam um par de ligações por bit para representar os valores lógicos desse mesmo bit, ou seja o seu valor binário, em oposição à comum ligação singular por bit, que também pode ser vista como Single Rail.

A implementação de circuitos usando codificações baseadas na duplicação de bits é extensivamente discutida pela comunidade académica, nomeadamente em artigo como [15],

27 [28]–[32], discutindo diversas formas de implementação, sendo muitas dessas considerações pensadas para ASIC.

As principais considerações estabelecidas nestes artigos centram-se na necessidade de tornar a actividade de transição da comutação dos transístores constituintes da lógica interna regular e na tentativa de evitar as glitches originadas por diversos factores, tanto da lógica como do sinal de relógio do circuito.

Desta forma ficam em aberto múltiplas alternativas relativas ao modo como o valor do bit será codificado. A escolha dessa codificação trará consequências, não só a nível da segurança efectivamente oferecida por esta implementação mas também a nível da área ocupada pelo módulo, devido, por um lado, às células modificadas e, por outro, à electrónica adicional, o que se reflecte no troughput expectável, por consequência dos atrasos induzidos pelo factor anterior.

Para além de múltiplas hipóteses de codificação dos bits, existem ainda diversas formas de implementar o conceito escolhido.

Nas próximas páginas serão expostas algumas das codificações propostas, nomeadamente as descritas no artigo [15] no qual o conceito de Dual Railling é extensivamente explorado como contramedida para defender implementações em hardware, no caso em ASIC mas permitindo aplicação dos conceitos em FPGA, do AES contra ataques de SCA explorando a leitura e análise do consumo. A exploração dos conceitos, no entanto, não referirá as arquitecturas propostas no artigo em análise uma vez que, muitas destas, não são directamente executáveis em FPGA.

Comece-se por analisar a codificação conhecida como Dual Rail Single Spacer. Esta pretende forçar a transição de valores constantes entre ciclos, existindo, independentemente do valor válido, uma transição de um dos rails por ciclo. Deste modo pretende tentar obter um traçado de consumo constante, com picos contantes durante as transições.

Para isso o DRSS toma como valores representativos os presentes na Tabela 7. Considera-se desse modo o spacer um valor inválido e não representativo de qualquer valor lógico.

28

Tabela 7 - Codificação Dual Rail Single Spacer

Valor Palavra

0 01

1 10

Spacer 00

O spacer, incluído nesta noção, é usado para forçar a transição constante de valores entre ciclos, obrigando ao regresso constante ao spacer entre valores válidos, como representado na Imagem 13.

Valor “0”

‘01’

Spacer

‘00'

Valor “1”

‘10’

Imagem 13 - Diagrama de Estados DRSS

Face a uma implementação sem qualquer tipo de codificação, também chamada Single Rail, as implementações deste género de lógica representam grandes overheads em termos da lógica necessária para a implementar.

Da mesma forma que o DRSS, o Dual Rail Dual Spacer tenta provocar a transição de pelo menos um bit de forma constante de modo a esconder picos diferenciados de consumo.

Tabela 8 - Codificação Dual Rail Dual Spacer

Valor Palavra

0 01

1 10

Zero Spacer 00

29 Ao contrário do DRSS o DRDS usa dois spacers distintos o Zero e o One spacer. Estes valores funcionam da mesma forma que o spacer singular do DRSS mas permite alternar sobre eles, ora de forma aleatória ou arbitrária ora de forma alternada.

No entanto as implicações da escolha do funcionamento ser arbitrária ou alternada implica mais consequências na definição do protocolo sendo espectável que a funcionar de forma arbitrária se possa ver a codificação mostrada na Tabela 8 segundo o comportamento descrito na Imagem 14.

Valor “0”

‘01’

Spacer

‘00'

Valor “1”

‘10’

Spacer

‘11'

Imagem 14 - Diagrama de Estados DRDS

Na tentativa de garantir um maior balanço energético bem como de reduzir o valor da possível informação recolhida, dificultando um pouco mais os ataques DPA, foi considerado ainda que, caso os spacer sejam percorridos de uma forma alternada se pode fazer depender o valor da palavra válida do spacer que a procede. Esses valores podem ser vistos na Tabela 9.

Tabela 9 - Codificação Dual Rail Dual Spacer Alternado

Estado anterior

Estado actual Entrada Estado seguinte Significado

XX 00 10 10 “1”

XX 00 01 01 “0”

00 XX XX 11 Spacer All-Ones

30

XX 11 01 10 “0”

11 XX XX 00 Spacer All-Zeros

Para usar esta mesma tabela de codificação é necessário seguir o diagrama de estados presente na Imagem 15, que indica o funcionamento do DRDS com spacers alternados.

Com este funcionamento a tentativa é garantir que para cada valor válido qualquer um dos rails usados no circuito comuta pelo menos uma vez obtendo desse modo um melhor balanço a nível energético.

Valor “0” ‘01’

Spacer

‘00'

Valor “1” ‘10’Spacer

‘11'

Valor “0” ‘10’ Valor “1” ‘01’Imagem 15 - Diagrama de Estados DRDS com valores alternados

O grande problema do uso de uma técnica como esta para proteger um sistema é, de facto, o overhead de área considerável que acarreta, nomeadamente a nível da lógica de controlo, e o que torna pouco exequível a sua implementação.

Incidindo sobre a necessidade de estabelecer um método mais efectivo que o original Dual Rail Single Spacer, mas com um overhead de área menor, e aproveitando os conceitos proposto em [15], em [33] Papadopoulos et al propõem um método novo de tentar conciliar a implementação de AES em hardware, com contramedidas efectivas contra ataques DPA, e o uso de FPGA de baixo custo na sua implementação.