Design, Analysis, Implementation and Synthesis of 16 bit Reversible ALU by using Xilinx 12.2

Texto

Imagem

Documentos relacionados

This is done by designing a Verilog program for a simple DSP application of ‘Inversion of bits’ on an 8 bit, 16 bit and a 32 bit processor assuming that the incoming audio signal

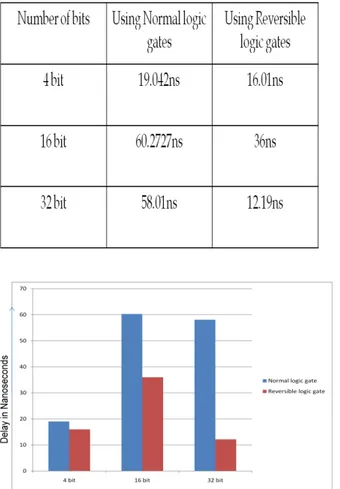

The adder has been simulated using verilog HDL codes and mapped this design to the TSMC (180nm) implementation technology using the Synopsys Design Complier and calculated the

In this paper, we have proposed a new design technique of BCD Adder using newly constructed reversible gates are based on NMOS with pass transistor gates, where the

From the comparative graph it is concluded that the performance of carry propagate adder based on gate diffusion input technique has a better performance than

In this paper, we are discussing basic reversible gates, algorithm of 2x2 vedic multiplier and 4x4 vedic multiplier and how it is optimized by reducing number of

In this paper we design a reversible Half Subtractor circuit by Feynman gate using QCA Technology.. The half subtractor performs

The proposed Full adder can be implemented using combination of all optical reversible NOR logic gate and using all optical reversible NAND gate (NAND logic based

In this paper design the 4-bit Vedic multiplier using different adder and implementation 8-bit radix-2 FFT algorithm.. The paper is organized as follows: Section II