IMPLEMENTATION OF VEDIC MULTIPLIER USING REVERSIBLE GATES

Texto

Imagem

Documentos relacionados

In this paper, we introduce the Orlicz sequence spaces generated by Ces` aro mean of order one associated with a fixed multiplier sequence of non-zero scalars.. Furthermore,

By inserting more number of zeros in the multiplicand using booth recoding unit we can reduce the switching activity by shutting down the idle part of the circuit

In this paper, we have proposed a new design technique of BCD Adder using newly constructed reversible gates are based on NMOS with pass transistor gates, where the

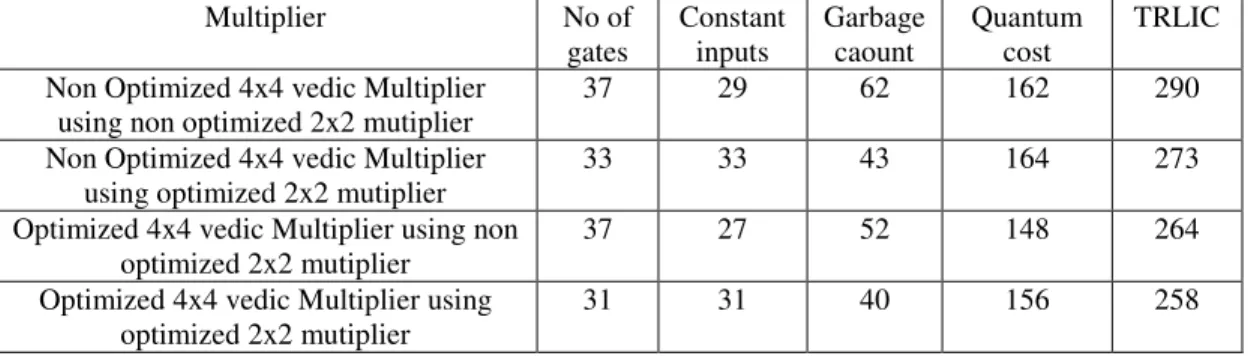

The multiplier, being the most significant block in many such digital systems, their speed and efficiency are primarily dependent upon the speed, area, throughput

Reversible logic c ircuits have the same number of inputs and outputs, and have one-to-one mapping between vectors of inputs and outputs; thus the vector of

Sediment transport in waterways towards dam reservoirs affects their life span by reducing their storage capacity and burying their bottom control gates and equipments. In this

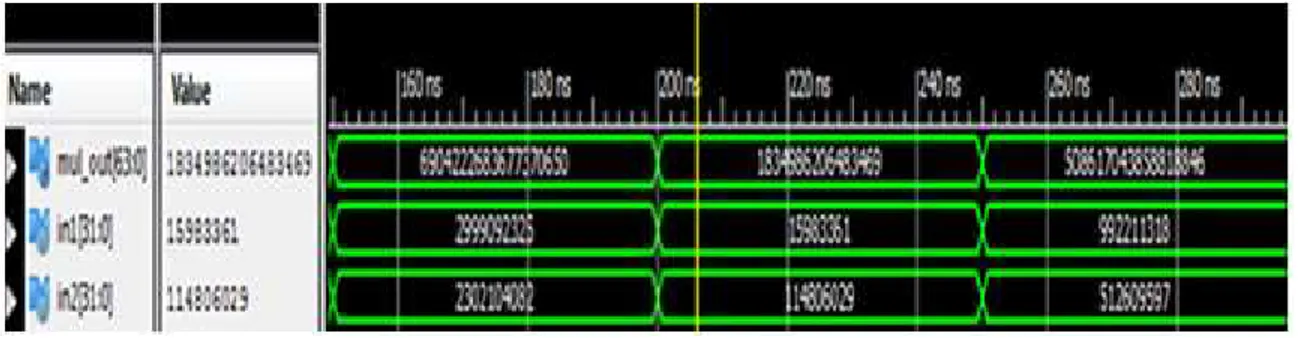

In this paper design the 4-bit Vedic multiplier using different adder and implementation 8-bit radix-2 FFT algorithm.. The paper is organized as follows: Section II

While comparing the performance results, it is found that the speed of the operation is increased in accumulator based Radix-4 multiplier by reducing the partial products