High Speed Area Efficient 8-point FFT using Vedic Multiplier

Texto

Imagem

Documentos relacionados

In section II the implementation of complex number multiplier using Gauss’s multiplication equations, and Urdhva Tiryakbhyam sutra of Vedic mathematics is explained with

Real-time signal processing requires high speed and high throughput Multiplier-Accumulator (MAC) unit that consumes low power, which is always a key to achieve a high

We have proposed a 128-point FFT processor, consuming low power and having small chip area using CMOS technology and to increase the processing speed based on

Reversible logic c ircuits have the same number of inputs and outputs, and have one-to-one mapping between vectors of inputs and outputs; thus the vector of

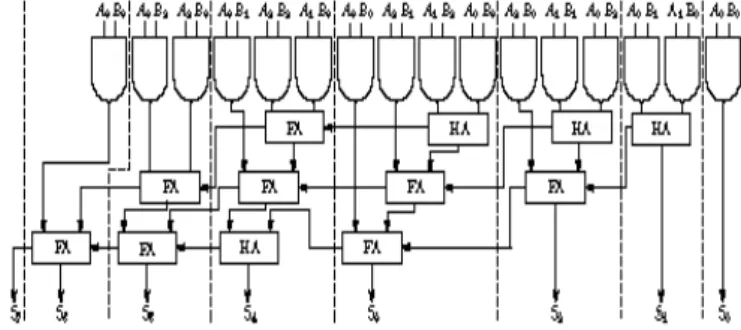

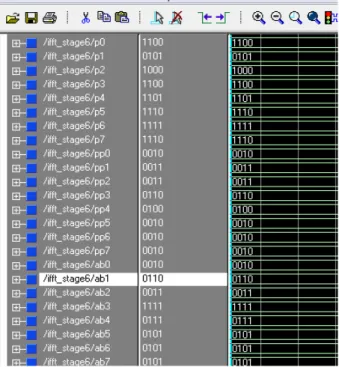

In this section, the result of the Kogge stone adder, Vedic multiplier and MAC unit are displayed using VIRTEX-4 family, XC4VFX140 device, 11FF1517 package, -11 speed.. Fig

In this paper, we are discussing basic reversible gates, algorithm of 2x2 vedic multiplier and 4x4 vedic multiplier and how it is optimized by reducing number of

A new technique of implementing a multiplier circuit using Decomposition Logic is proposed here which improves speed with very little increase in power dissipation when compared

The multiplier, being the most significant block in many such digital systems, their speed and efficiency are primarily dependent upon the speed, area, throughput